基于DSP的高速数据传输系统研究与设计毕业论文

2020-02-19 07:57:19

摘 要

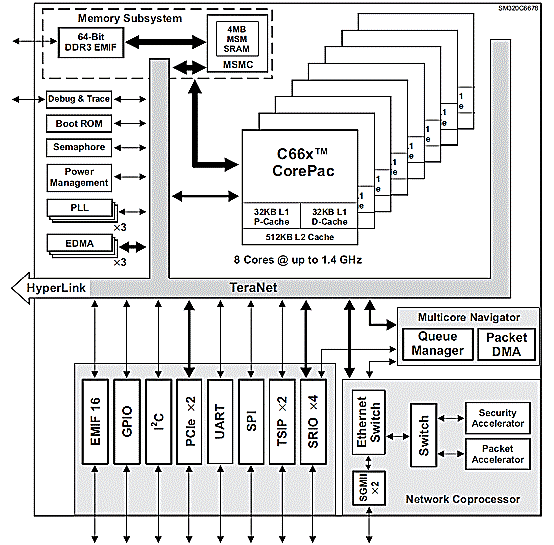

传统的图像数据传输系统负责进行图像数据传输,目前广泛应用于市场上。随着数据量的增多,系统内部数据交互的带宽随之上升,现有的系统无法满足通信、检测、图像处理领域的需求,高速数据传输系统的设计越发重要。本文基于常用的DSP FPGA异构处理器搭建高速数据传输系统,采用分段传送数据的方式。FPGA对数据的预处理后,采用高速串行接口进行通信,利用中断响应机制传输至DSP,然后通过DMA方式传送给外接DDR3,实现芯片间高速数据传输和共享存储的功能。

本文通过对比传输方案选择了SRIO接口总线技术,依靠其强大的带宽以及灵活的连接方式,结合新型FPGA和DSP芯片功耗、处理性能、片间传输速度的优势,以获取更加快速的传输速度和更加短暂的处理时间。且该系统保留了FPGA DSP的架构,使其具有普遍应用的可能性。本文使用xilinx和ti公司的芯片调试软件结合硬件进行设置和编程实现系统高速通信。通过抓取芯片内部存储数据和测试传输速率证明了本文设计的系统能够满足工作需求。

关键词:FPGA;DSP; SRIO;传输

Abstract

The conventional image data transmission system is responsible for image data transmission and is currently widely used in the market. As the amount of data increases, the bandwidth of data interaction within the system increases, and the existing systems cannot meet the needs of communication, detection, and image processing. The design of high-speed data transmission systems becomes more and more important. This paper builds a high-speed data transmission system based on the commonly used DSP FPGA heterogeneous processor, and adopts the method of segmenting data transmission. After preprocessing the data by the FPGA, the high-speed serial interface is used for communication, and the interrupt response mechanism is used to transmit to the DSP, and then transmitted to the external DDR3 through the DMA method to realize high-speed data transmission and shared storage between the chips.

This paper selects the SRIO interface bus technology through the comparison transmission scheme, and relies on its powerful bandwidth and flexible connection method, combined with the advantages of new FPGA and DSP power consumption, processing performance and inter-chip transmission speed, in order to obtain faster transmission speed and more. Short processing time. And the system retains the architecture of FPGA DSP, making it universally applicable. This article uses xilinx and ti's chip debugging software combined with hardware for setup and programming to achieve high-speed system communication. By grasping the internal storage data of the chip and testing the transmission rate, it is proved that the system designed in this paper can meet the work requirements.

Key word: FPGA;DSP; SRIO; transmission

目 录

第一章 绪 论 1

1.1 研究背景 1

1.2 研究现状 1

第二章 方案设计 4

2.1 总体方案设计 4

2.2 传输技术方案 5

2.3 芯片选型 6

2.3.1 FPGA芯片选型 6

2.3.2 DSP芯片选型 7

第三章 接口和电源时钟模块 9

3.1互连接口 9

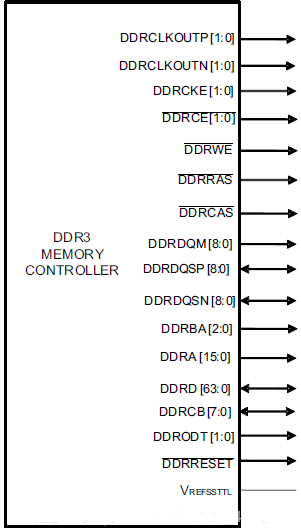

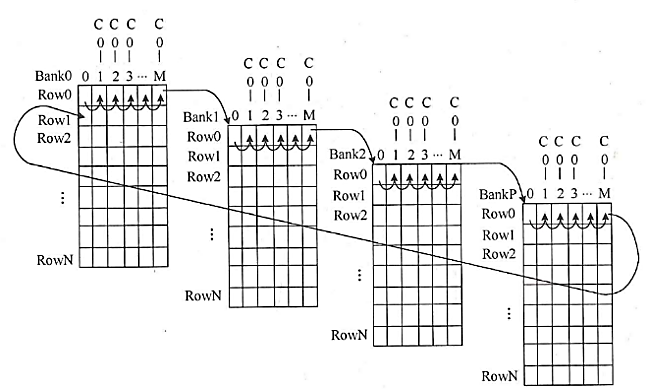

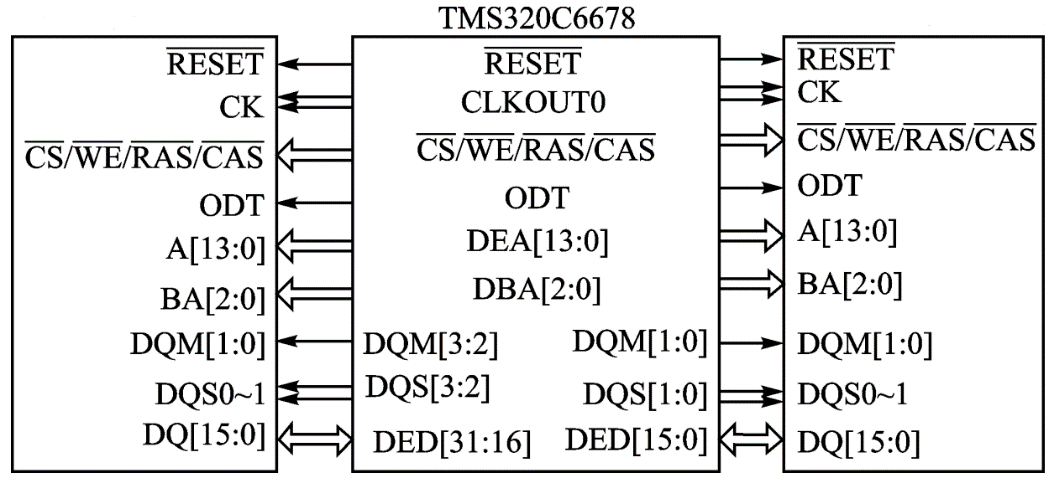

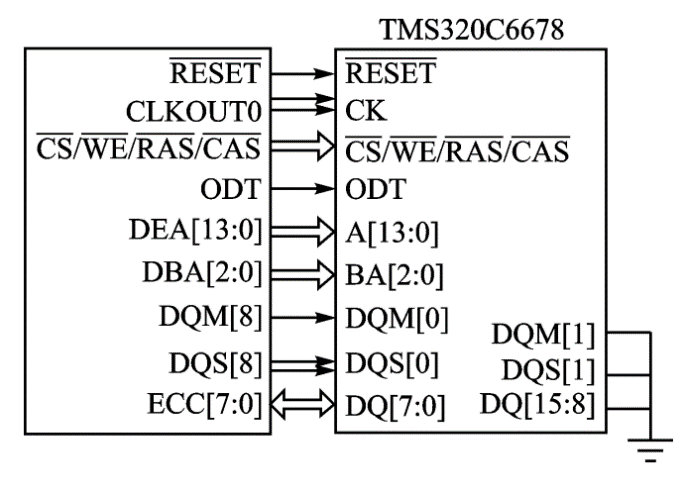

3.1.1外接存储器接口 9

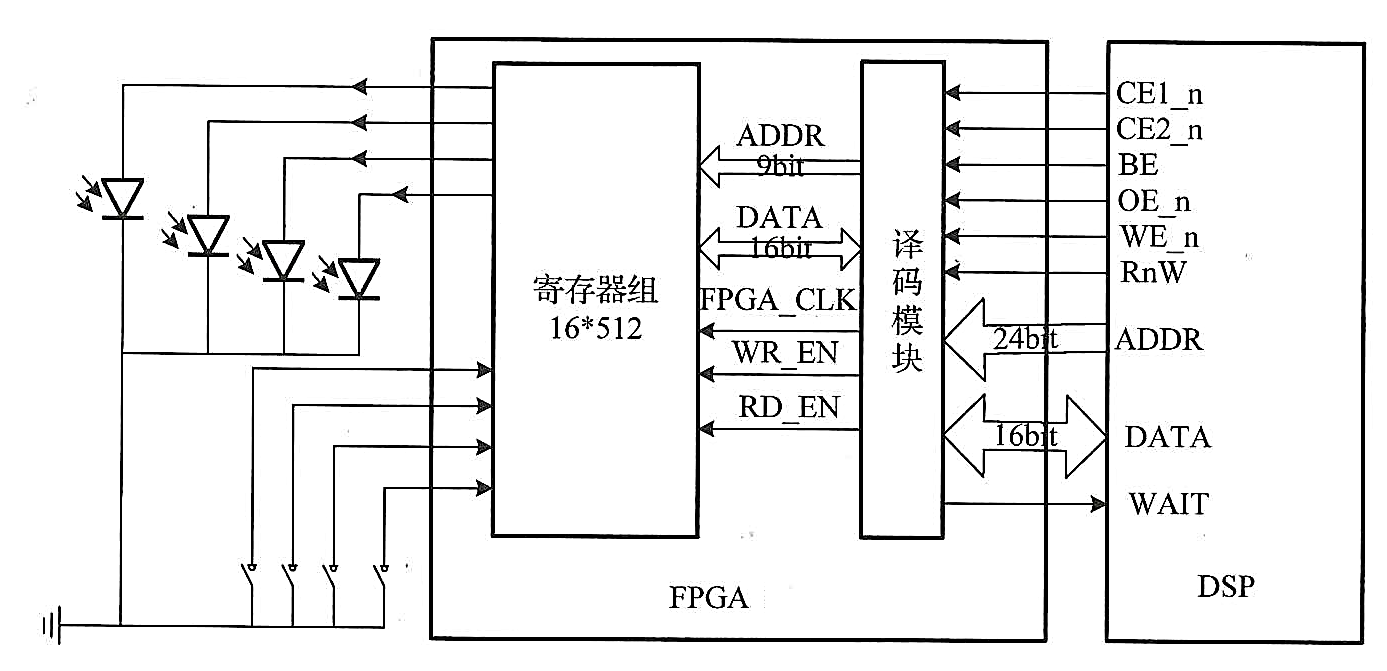

3.1.2 芯片间EMIF接口 13

3.1.3 RapidIO接口 14

3.1.4 PCIe接口 14

3.2 电源和时钟模块 15

3.2.1 电源设计 15

3.2.2 时钟设计 17

第四章 处理器间不同接口的通信实现过程 19

4.1 EMIF接口通信实现过程 19

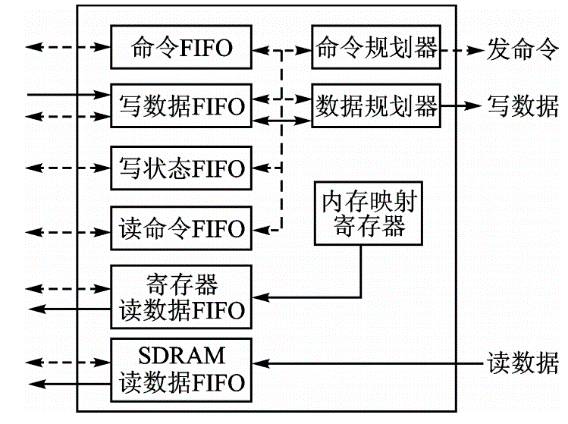

4.2 RapidIO通信实现过程 21

4.2.1 FPGA的通信实现过程 21

4.2.2 DSP的通信实现过程 24

4.3 PCIe通信实现过程 26

第五章 系统传输测试 28

5.1传输测试 28

5.2 芯片间通信效率 30

第六章 总结与展望 37

参考文献 38

附 录 39

第一章 绪 论

1.1 研究背景

随着数字信号处理技术的发展,人们越发注重生活素质,人们开始追求更“快速”更“清晰”的生活,“快速”指的是数据传输的速度,“清晰”指的是图片、视频的分辨率。人民的需求提升使得传感器技术得以迅速发展,系统处理的数据更加庞大和复杂。图像数据量的激增除了对数据处理系统的计算能力有更高的要求,也给处理芯片间的数据传输带来了挑战。目前,嵌入式数据处理系统常用的传统传输互连总线技术无法满足芯片间高速数据传输的需求,设计高速数据传输系统刻不容缓。

设计高速数据传输系统除了能满足人民生活的需求,更快速的传输数据外,更是为了实现多处理器间的快速数据传输、高速数据交互和共享存储的功能,以及解决传统数据传输系统带宽不足的问题,对图像数据传输系统的发展和应用具有重大现实意义。

1.2 研究现状

图像数据传输系统根据信号类型分为两个阶段[1]。

第一阶段在20世纪末,系统处理模拟信号。传感器采集到图像数据后,将卡带拔下,插入处理器中进行处理。系统不够智能,处理时间久。

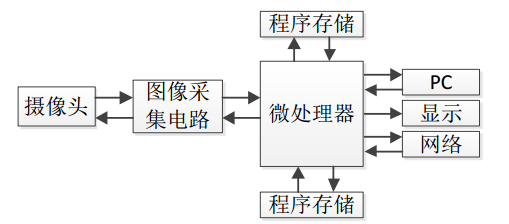

第二阶段是21世纪伊始至今是数字信号处理阶段。一开始系统采用的单芯片作为处理器。图像数据经过经由转换芯片处理后传送至处理器中处理。根据需求的不同组建电路,最典型的系统如图1.1所示。

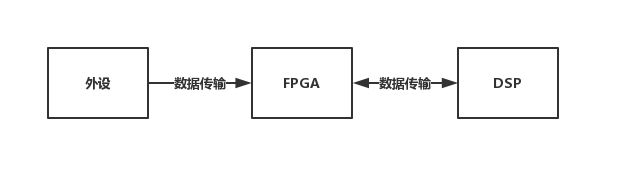

图1.1 单芯片系统

这种图像数据处理系统优点是:适应性强、集成度高、低功耗。只使用一个芯片作为处理器缺点如下:

(1)DSP并行处理能力效率低;

(2)低单片机处理能力低;

(3)FPGA实现算法困难。

在基于单芯片的基础上,发展了多芯片处理系统。结合不同芯片的特点,组成异构处理器作为系统的处理模块。这种架构通过各个芯片分工合作,分段进行操作,发挥其优势,加快系统的传输和处理速度。在这么多的嵌入式系统处理器架构中,DSP FPGA异构处理器架构具有最佳的性能。

基于异构处理器系统架构的数据传输处理系统性能随着DSP、FPGA芯片的更新换代而提升。DSP FPGA架构的图像处理系统将这两个芯片的优势互补,使系统并行和运算处理能力得到有机结合。性能如此强大的处理系统得到了广泛的关注。

随着系统应用在不同的领域,大量高分辨率和高帧率的前端设备将大量的数据传送回图像数据传输和处理系统[2]。因此如何实现系统高速传输数据和处理成了关键性的问题。目前,国内外的学者和工程师对图像数据传输和处理系统领域在进行研究,也取得了一些成果,但是还有许多问题亟待解决,需要进一步的研究。

李文磊等提出了基于PCI总线互连芯片传输数据。外联存储器存满时,从存储器中取出采样数据,使用DMA的方式经由PCI接口发送到总线中[3]。

吴长坤等基于USB3.0技术,通过FPGA实现高速数据传输。使用互连和传输接口EMIF共享总线技术,使用FPGA芯片模拟数据源,使用DDR2缓存,然后使用USB3.0接口发送至上位机,处理器获得数据后,实现实时处理、实时监测、实时控制的功能[4]。

Emilio J. Bueno等人使用异构处理器通过EMIF接口传输数据,与固定点DSP相比,FPGA在重复和大规模计算中提供更高的性能,从而缩短了执行时间,该方案通过FPGA先对数据进行预处理,再传输到DSP处理器中进行处理,减少处理时间[5]。

近几年,数据处理系统的实时性和高速性越发重要。处理器间交互程度更紧密,传输速度更快是数据传输及处理系统发展的方向。因此采用高性能的处理器芯片和合理的处理器结构以及更高速的传输方式将是发展的趋势。

图像处理系统中FPGA和DSP之间属于优缺互补,共同完成图像处理任务。虽然使用异构处理器使得系统的运算能力和数据传输速度有所加强,但是随着芯片需要进行的算法复杂度提升、交互数据增多,传统的总线技术的频率和接口宽度太小,无法满足大带宽数据的传输[6]。异构处理器架构的数据处理系统面临着传输交互的带宽问题。

如果图像数据处理系统有多路输入接口,那么芯片间交互的速率至少以Gb/s为单位。芯片需要处理的数据量的增加,给芯片交互带来了压力。传统的接口互连传输无法满足目前系统的数据交互需求,成为了图像处理系统发展的瓶颈。

随着信号处理的带宽需求不断增长,目前单芯片的处理速度已无法满足实时处理系统性能要求。TI公司的多核DSP处理性能强大,然而无法在并行处理要求高的场景中完美运行。FPGA并行处理能力强,接口丰富,但是无法进行复杂的运算。结合不同芯片的特性,构建基于异构处理器的数据处理系统,以高速传输接口技术作为芯片间的通信方式,实现高速数据传输系统的设计。本文基于DSP与FPGA架构结合高速传输互连接口设计的高速数据传输系统,可以提高处理器芯片之间数据交互传输的速度,为嵌入式系统内部芯片互连提供了良好的解决方案。

第二章 方案设计

2.1 总体方案设计

本文基于高速互连接口和双芯片异构处理器进行高速数据传输系统的设计。以DSP为主处理器,FPGA为协处理器,如图2.1所示。FPGA对外接口接收外部设备传入的的图像数据,通过高速接口将数据传输至DSP。外部输入的数据经过FPGA的预处理后再传至DSP中进行处理,充分运用两种芯片不同的性能特点。

图2.1 DSP与FPGA的通信示意图

为突破原有芯片和传输方式的局限性,本文在高速数据传输系统中采用了以下技术和方法。

(1)采用新一代FPGA芯片

相较于之前的FPGA,新款FPGA芯片重新组建架构,降低芯片的消耗,提升了系统的整体性能;

(2)使用高速数据传输技术

为了解决系统内部芯片之间数据传输带宽不足,切实解决带宽限制。我们采用高速数据传输技术,从而实现芯片之间、系统之间数据 Gbps 级的快速稳定交互;

(3)使用新型高速数字信号处理器

TI公司新推出的DSP芯片的运算速度达到1Gbps以上。相对于前代的 DSP,新款芯片增加了支持SRIO或者PCIE的接口。芯片内置的高速传输互连接口的存在使得异构处理器之间能通过接口传输实现高速数据传送;

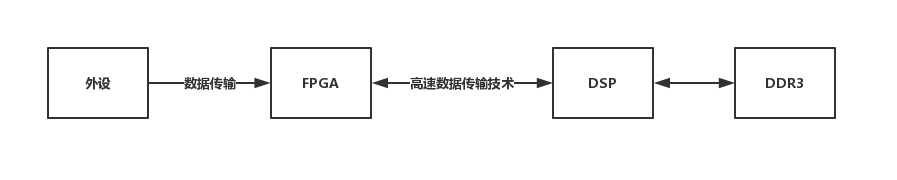

通过外连DDR3使得新系统具有共享存取的功能。通过这共享存储和高速传输互连接口技术的应用,使得系统对数据传输和处理速度得到提升。图2.2为系统的示意图。

图2.2 新系统示意图

系统的数据流程走向是:首先输入数据,模拟信号经过AD转换芯片的转换后或者直接将数字信号发送至协处理器中。协处理器上将数据重组配合包头信息小的指令进行传输,减小传输信息量来提高了传输速度[7]。在主处理器需要使用数据的时候,使用响应中断和预定义接收端数据存储单元与协处理器进行通信。芯片间通过高速接口将数据实时传输。芯片间通过EDMA的方式直接对DDR3存储器进行读写访问,不通过内核CPU读写,有效提升系统性能。

针对高速数据传输系统的系统特性,本文采用了FPGA DSP架构,搭建了基于FPGA芯片和高速处理器DSP芯片由高速数据传输接口进行通信的数据传输处理系统。

2.2 传输技术方案

传统的处理器之间互连采用并行总线,为了提高效率,并行总线需要增加总线位宽并提高时钟效率,这使得系统的结构更为复杂,生产成本更高昂。并行总线实现高速传输复杂且昂贵,高速串行互连方式是解决这些问题的有效方法。高速的传输方式主要有PCIe和Serial RapidIO(以下称SRIO)互连技术,这两种技术标准都是用相似的串行解串器(SerDes)技术。SRIO和PCIe在应用方面有所不同,SRIO更多用在嵌入式领域,而PCIe多应用于PC和服务器领域,但其也适合芯片间和背板互连。

PCI Express(PCI E)总线是在PCI(Peripheral Component Interconnect)总线的基础上发展而来的,使用高速串行传输方式[8]。相对并行传输,高速串行传输可以使用更高的时钟频率,从而使用更少的信号完成之前需要许多单端并行数据才能达到的总线带宽。PCIe是一种点对点、全双工、基于包结构的高速差分串行总线。PCIe发送数据时采用DLLP法,需要等待回复信号之后才发送下一次的数据包。PCIe传输速度较快,可靠性高,有着巨大的发展潜力。

SRIO体系结构是为了满足高性能嵌入式系统的独特需求发展的,即专门解决系统内互连问题[9]。SRIO网络由终端器件和交互器件组成,根据器件设置的ID号进行通信。SRIO将控制符放在数据包内一起传输,能够实现低延时数据交互,芯片间能更快地发送更多的数据包。SRIO是一种对等结构,支持任意的拓扑结构,非常适合多处理器的互连。

随着SRIO技术规范的完善,相应产品不断发布,产业链逐渐完整,RapidIO 的生态系统得以建立。FPGA和DSP芯片厂家目前生产且被市场广泛采用的 FPGA和DSP芯片均支持SRIO传输技术和PCIe传输技术。PCI Express接口管脚多、耗能强,且没有错误管理机制。SRIO传输方式却有冗余和错误管理机制,因此,SRIO比PCI Express优势更明显。SRIO接口互连传输技术更适合本系统的设计。本系统采用SRIO传输技术来实现芯片间的通信。

2.3 芯片选型

本文设计的系统中,芯片是整个系统的核心部分。芯片不仅要能满足运算能力强,实时性高等需求,还要能结合构成异构处理器架构形成核心处理器模块。因此对核心芯片的选择十分重要。

2.3.1 FPGA芯片选型

FPGA(场可编程的逻辑门阵列)设计灵活、逻辑资源丰富,不适合复杂的算法[10]。由于FPGA硬件电路的特殊性,其能进行并行数据传输。另外FPGA的电路可以进行编程,具有灵活性。所以本系统中FPGA负责前端并行数据预处理。对于核心器件FPGA的选取,需要满足以下要求:

1)自带高速数据传输互连接口,能满足实现FPGA与DSP对接;

2)丰富的IO接口;

3)芯片功能强大,能外接缓存;

4)性价比高;

Xilinx是FPGA芯片的主要生产产商。 FPGA芯片内部构造主要包括:

1) 可配置逻辑功能模块;

2) 可编程输入输出模块;

3) 可编程内部互连资源;

4) 存储器资源(BlockRAM);

5) 数字时钟管理模块;

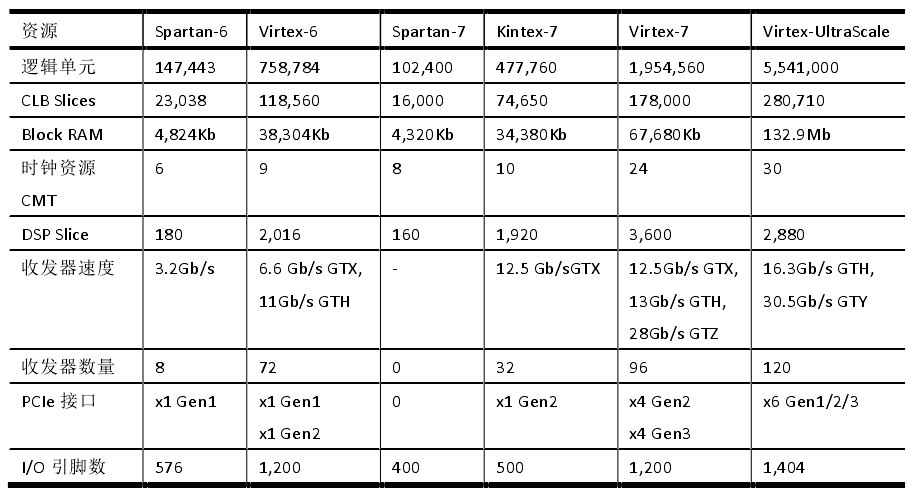

除了上面的几个基本构成部分之外, FPGA还会包含算术运算单元、内嵌专用硬核等。 目前主流的FPGA 系列芯片如表2.1所示。

表2.1 Xilinx FPGA 主流系列芯片的资源配置情况

从表2.1可知,Spartan 系列主要用于低成本应用,性能一般;Kintex 系列性价比高。Virtex 系列系统性能最强。赛灵思公司拥有无比丰富的FPGA芯片和相关产品,可以根据用户的需求进行选择或定制。

协处理器要实现需要采集、处理大量的数据信号及逻辑控制等功能,其自身需要具有较强的性能。针对上述要求,调查了FPGA 芯片特性及价格,选用了XC6VLX550T芯片。该芯片基于硬件GTX串行收发器可以实现多种高速数据传输接口采用IP核可以实现FPGA和DSP之间的SRIO协议通信

2.3.2 DSP芯片选型

DSP芯片是专门为了数字信号处理而设计的高速芯片[11]。本系统核心处理器便是DSP,其性能关系着系统运算能力的强弱。该芯片能具有可编程、处理速度快的特性。由于芯片处理算法的特点,以及芯片交互的实时性需求,系统选用的DSP应该具有以下特点:

1)拥有高速传输互连,能与其他芯片进行高速数据交互;

2)具有高性能、高效率的算法处理能力;

3)具有支持高速缓存器的接口;

4)芯片功能强大,开发简易,性价比比高;

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示: