智能数字日历设计与仿真毕业论文

2020-04-12 08:47:43

摘 要

随着时代的发展,科技的进步,日历不仅在我们的日常生产、生活中必不可少,而且它的内容、形式也越来越丰富。在高速发展的现代社会,传统的机械日历由于其在体积,机械结构,供电的限制,其功能和性能上已逐渐不能满足人们的工作、生活,各种电子化、智能化,多功能的日历应运而生。本课题是基于EDA工具设计一款数字智能日历,具有年、月、日、星期、时、分、秒计时显示功能、时间调整功能和整点报时功能,同时增加闹钟功能。

本设计从闹钟模块与整点报时模块、平、闰年调节模块、数码显示模块三个模块入手,将选用VHDL硬件描述语言,用VHDL完成各模块程序的设计,实现其功能编译和仿真,并在Quartus 2上完成整体的整合,实现其功能的编译和仿真。

本设计能够实现年、月、日、时、分、秒计时显示功能,同时能够识别平,闰年并且自动调整对应月份的天数,能够完成时间调整能功能、整点报时功能以及闹钟功能。它能满足了大多数人对日历功能的要求,大大的方便了人们的生活。

关键词:智能日历,VHDL,Quartus 2,EDA

Abstract

With the development of The Times and the progress of science and technology, calendar is not only indispensable in our daily production and life, but also more and more rich in content and form. In the rapid development of modern society, the traditional mechanical calendar due to its size, the mechanical structure, the limitation of power supply, its function and performance has been gradually cannot satisfy people's work and life, all kinds of digital, intelligent, multi-function calendars came into being. This topic is based on EDA tools to design a digital smart calendar, a year, month, day, week, time, minutes and seconds when display function, the time adjustment function and function of hour, at the same time increase the alarm clock function.

This design from the alarm module and hour module, flat, leap year adjustment module, digital display module three modules, this paper will use VHDL hardware description language, complete each module program design with VHDL, compilation and simulation to achieve its function, and with the overall integration on Quartus 2, realize the function of the compilation and simulation.

This design can achieve the year, month, day, hours, minutes, seconds time display function, at the same time able to identify, leap year and automatically adjust the corresponding to the number of days in February, able to complete time adjustment function, the integral point to announce the correct time and alarm clock function function. It can meet the requirements of most people on the function of calendar and greatly facilitate people's life.

Keywords: smart calendar,VHDL, Quartus 2, EDA

目录

摘要 I

第1章 绪论 1

第2章 系统结构与方案设计 3

2.1系统结构 3

2.2方案设计 4

2.2.1 课题分析 4

2.2.2方案选择 4

2.2.3硬件描述语言选择 5

2.2.4 设计环境选择 5

2.2.5方案设计小结 6

第3章 闹钟模块与整点报时模块 7

3.1模块设计 7

3.1.1 秒模块 7

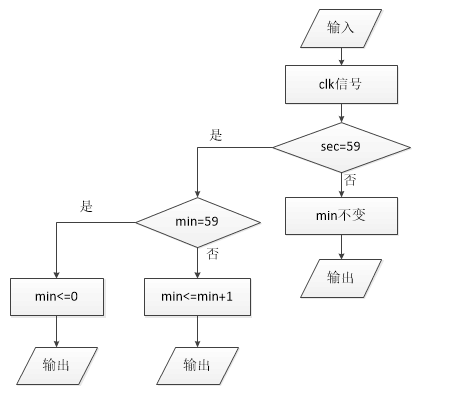

3.1.2 分模块 8

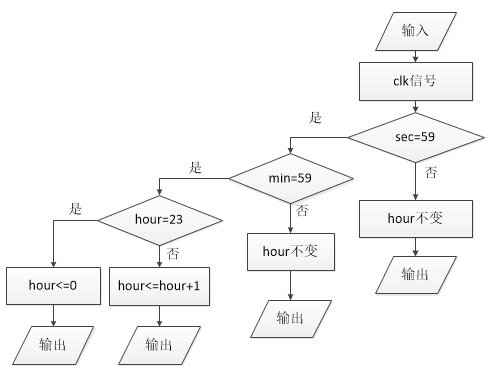

3.1.3 时模块 8

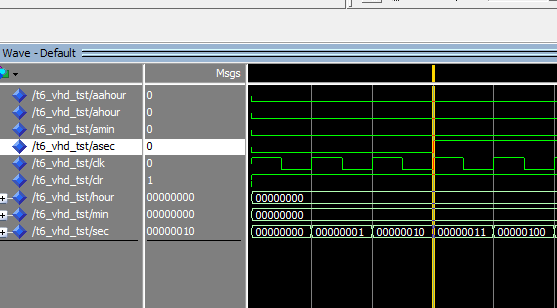

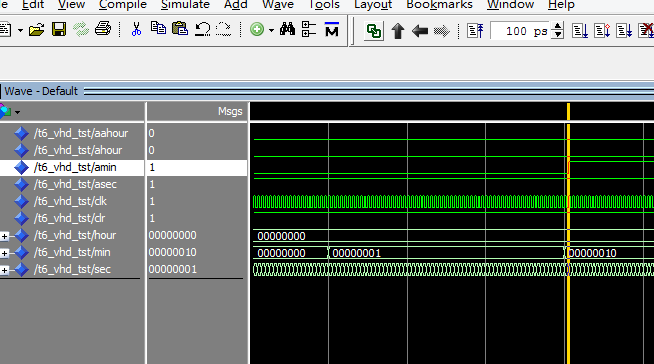

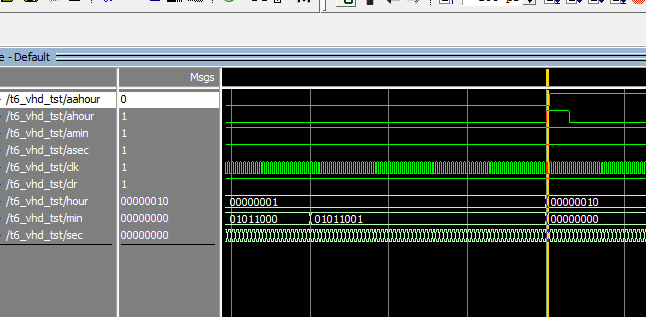

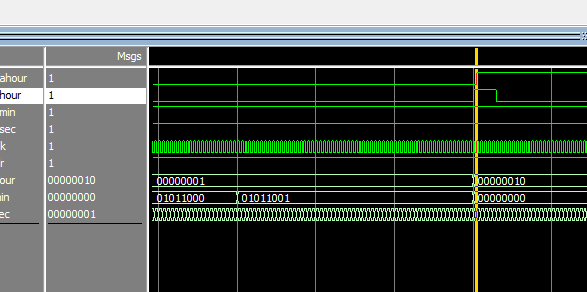

3.2 模块仿真 9

第4章 平、闰年调节模块 11

4.1 系统分析 11

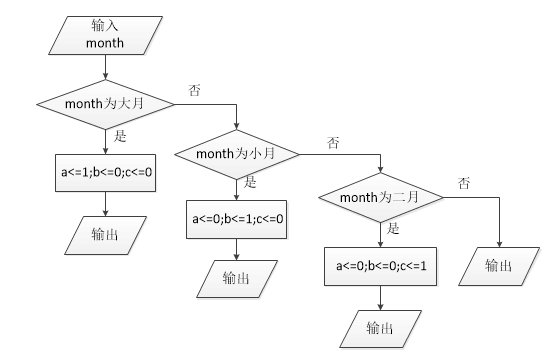

4.2 年,月,日模块 11

第5章 数码显示模块 15

5.1设计分析 15

5.2程序设计 15

第6章 系统仿真 17

6.1 仿真程序及图形 17

6.2 结果分析 20

第7章 结论 21

7.1 总结 21

7.2 展望 22

致谢 23

参考文献 24

附录 25

第1章 绪论

随着时代的发展,科技的进步,日历不仅在我们的生产、生活中必不可少,而且它的内容和形式也越来越丰富。在高速发展的现代社会,传统的机械日历由于其在体积,机械结构,供电的限制,其功能和性能上已逐渐不能满足人们的工作、生活,各种电子化、智能化,多功能的日历应运而生。本课题是基于一种EDA工具设计的智能数字日历,不仅具有传统日历年、月、日、星期、时、分、秒计时显示功能,同时,它还能智能化的判断当前的年份(平年和闰年)自我调整,另外它还加上了时间调整功能、整点报时功能和闹钟功能。它能满足了大多数人对日历功能的要求,大大的方便了人们的生活。

自从单片机的广泛运用,各种各样的多功能电子日历相继问世。目前,国内的数字日历技术向着超微型、超高效的方向发展,它内部的核心元件是单片机,主要由运算器,控制器,寄存器组成,其使用方便,能实现模块化,可靠性高,处理功能强,速度快,低电压,低功耗,便于生产便携式产品,控制功能强,环境适应能力强,单片机的运用使得日历在其功能,性能等方面获得了大大的提升,使其具有体积小,损耗小,使用寿命长、计时精准、性能稳定、兼容性强,使用界面简单,功能扩展方便,维护更换方便等特点,被广泛运用于医学仪器,电子科学仪表,办公会议,工作车间,科学探索等场合,北京天诚瑞达时钟科技有限公司生产的新一代数字时钟,它是以单片机作为控制核心模块,以输入脉冲电路,晶振电路,复位电路,按键电路,外部存储器电路,蜂鸣器电路,闹钟模块,显示模块电路作为主要电路,可根据用户需要添加多种不同的功能,例如自动报警、定时、日期查询等多方面功能,相当人性化,开发设计的电路简单,可靠性强,实时性好,时间精准性高,操作简单。

在国外,数字日历技术的趋势在于将系统模块化,实时计时,它功能强大,形式多样,性能稳定,计时更为精确,续航能力强等特点,目前使用比较广泛是美国的DALLAS公司推出了一块实时时钟芯片DS1302,它一种高性能、低功耗的实时时钟芯片。该芯片在其结构上附加了31字节静态 RAM,能够与内部 CPU进行同步通信,可以在同一时刻传送多个字节的时钟信号和 RAM数据,使得计时更为精准。以DS1302为核心的实时日历可提供秒、分、时、日、星期、月和年的显示,且具有闰年补偿功能。该芯片采用双电源供电,可设置备用电源充电方式,能够对后备电源进行涓细电流充电,使得它具有很强的续航能力和精准性。这种结合DS1302芯片的电子日历功能丰富,它对时间的计算更为精准,也具有分辨平、闰年的功能,另外,芯片的引入,减少了其机械结构,也使得其使用寿命大大增加,同时,其结构的模块化也使得其能包括更多的功能,例如:闹钟功能,现实环境温度的功能等。

本课题是基于一种EDA工具设计的智能数字日历,利用VHDL硬件描述语言的强大的电路描述和建模能力设计的智能日历,相比于那些利用多种组合逻辑电路和和时序电路等小型集成电路来设计的,它的硬件构成会相对简单许多,也更有利于后面功能上的扩展和测试维护;相比于那些基于单片机来设计的系统,它是将传统数字系统设计中的搭建调试用软件仿真取代,用硬件描述语言在计算机上建立的系统模型,用测试码验证后,将其实现在专用集成电路上,实现了程序语句与硬件元件的统一,很大程度上地提高了设计者对于电路设计的效率,大大缩短了设计和开发时间,大大降低了人力成本,提高了系统的稳定性,方便维护。

第2章 系统结构与方案设计

2.1系统结构

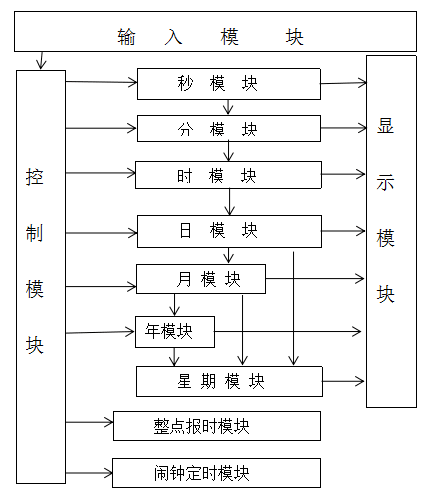

本课题是基于EDA工具设计一款数字智能日历,具有年、月、日、星期、时、分、秒计时显示功能、时间调整功能和整点报时功能,同时增加闹钟功能。 将要设计的系统分为以下几个模块:输入模块、控制模块、整点报时模块、闹钟定时模块、秒模块、分模块、时模块、日模块、月模块、年模块、星期模块以及显示模块,系统总模块图如图2-1所示:

本课题是基于EDA工具设计一款数字智能日历,具有年、月、日、星期、时、分、秒计时显示功能、时间调整功能和整点报时功能,同时增加闹钟功能。 将要设计的系统分为以下几个模块:输入模块、控制模块、整点报时模块、闹钟定时模块、秒模块、分模块、时模块、日模块、月模块、年模块、星期模块以及显示模块,系统总模块图如图2-1所示:

图2-1 系统总模块图

如系统模块图所示,先经过输入模块输入当前时间,用控制模块控制秒模块,分模块分别使用计数器进行0到59循环计数,控制时模块使用计数器进行0到23循环计数,日模块采用一个选择计数器选项为28、29、30、31,大月选择31,除2月的小月选择30,平年的2月选择28,闰年的2月选择29,用控制模块来做到辨别闰、平年以及大小月份,确定选择计数器的值,同时也给出整点报时和闹钟定时模块的触发信号。整点报时模块和闹钟定时模块分别连接一个蜂鸣器电路,当整点时,控制模块给出信号整点报时模块进行报时,当预设的定时时间到来时,控制模块给出信号,闹钟模块启动。显示模块使用多的片选芯片,每个片选信号控制一个晶体数码管,每个片选信号表示一位时钟输出信号,再利用转换代码将四位的BCD码转换成七位的晶体数码管显示码,发送给对应的晶体数码管实现显示时间。

2.2方案设计

2.2.1 课题分析

本课题是基于EDA工具设计一款数字智能日历,具有年、月、日、星期、时、分、秒计时显示功能、时间调整功能和整点报时功能,同时增加闹钟功能。本设计将会运用EDA技术来完成,EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

基于EDA设计的系统的最大优势是,在设计的一开始,设计者并不需要过多的了解系统所需硬件方面的结构,便可以根据系统所要实现的功能从程序控制方面直接开始设计系统的逻辑结构以及优化算法。利用一些标准化的硬件描述语言,将大部分基础的模块硬件结构设计由计算机自动生成,并且生成的模块可以保存入库,可供以后的工程中重复调用,从而很大程度上地提高了设计者对于电路设计的效率,大大缩短了设计和开发时间。

2.2.2方案选择

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示: