基于多脉冲合成的超短脉冲高精度回波重构技术研究毕业论文

2020-02-19 07:53:13

摘 要

半导体激光器的发展推动激光器在各领域的迅猛发展。在脉冲式数字激光雷达测距系统中,脉宽一般为几十纳秒。提高飞行时间测量精度和信噪比的前提是不失真的对超短脉冲激光回波信号进行采集和存储,保证数据的完整性。高频ADC不仅价格昂贵,也存在有一定的技术封锁。所以,本文提出了一种利用发射脉冲间隔调制的方法来实现低速模数转换器的高频采样,其时间测量的精度取决于调制脉冲周期与采样周期之间的关系。利用50M的低频ADC,通过脉冲间隔调制,将重构精度提高的625ps(等效采样率1.6G sps),可以满足中长距激光雷达的测量精度。此外,脉冲式激光雷达是通过测量反射波的时间延迟来计算目标物体的距离,而回波信号强度会随距离的增加而衰减,有用信号被噪声掩盖,造成测量误差。为提高激光雷达的探测范围,就必须提高雷达系统的信噪比。本文通过数据累积来提高激光雷达回波信号的信噪比。仿真和实验结果均表明此方法的可取性。并且验证了数据累积对于提高信噪比的有效性。

关键词:超短脉冲;信号重构;降噪方法

Abstract

The development of semiconductor lasers promotes the rapid development of lasers in various fields. In pulsed digital lidar ranging system, the pulse width is tens of nanoseconds. The premise of improving the accuracy of flight time measurement and SNR is to collect and store ultrashort pulse laser echo signal without loss of authenticity to ensure the integrity of data. High frequency ADC is not only expensive, but also has some technology blocking. Therefore, a method of transmitting pulse interval modulation is proposed to realize high frequency sampling of low speed

ADC. A 50M low-frequency ADC is used to improve the reconstruction accuracy of 625ps through pulse interval modulation, which can meet the measurement accuracy of medium-long distance lidar. In addition, pulsed lidar calculates the distance of the target object by measuring the time delay of the reflected wave, while the echo signal strength decreases with the increase of the distance, and the useful signal is covered by noise, resulting in measurement error. In order to improve the detection range of lidar, the signal-to-noise ratio of radar system must be improved. In this paper, the signal to noise ratio of laser radar echo is improved by data accumulation. Simulation and experimental results show that this method is feasible. The effectiveness of data accumulation in improving SNR is verified.

Keywords: ultrashort pulse; Sampling method; Signal reconstruction

目 录

·第一章 绪论 1

1.1研究背景以及意义 1

1.2 国内外研究现状 2

1.3 课题研究内容 3

第二章 多脉冲合成的超短脉冲高精度回波重构方法研究 5

2.1 顺序采样法 5

2.1.1 顺序采样原理 5

2.1.2 顺序采样具体步骤 6

2.2 交错采样法 6

2.2.1 交错采样原理 6

2.2.2 交错采样具体步骤 7

2.3 顺序采样方法和交错采样方法比较 7

2.4 增强信噪比SNR的方法 7

第三章 多脉冲合成的超短脉冲回波重构系统软件设计 9

3.1 发射脉冲调制算法原理 9

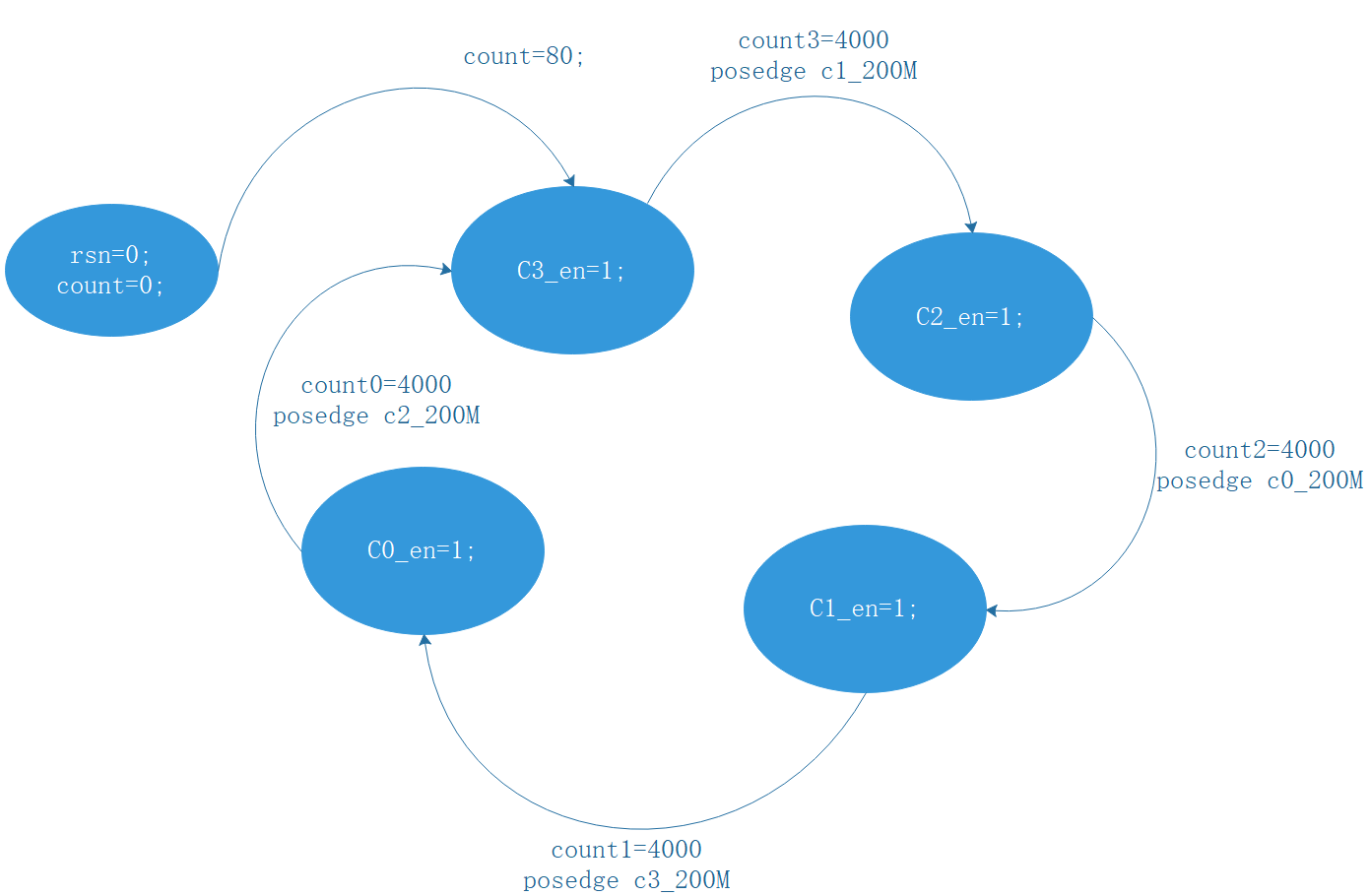

3.2 发射脉冲调制算法程序状态转换图 11

3.3 回波重构算法原理 12

第四章 多脉冲合成的超短脉冲回波重构系统硬件设计 13

4.1 FPGA 13

4.2激光发射模块 15

4.2.1 激光整形电路DS1100L 15

4.2.2 激光驱动器MAX15024 16

4.2.3 激光发射器SPLLL90 17

4.3 激光接受模块 17

4.3.1 光电探测器 BPW34BS 18

4.3.2 前置放大器MAX3806 18

4.3.3 高速比较器 ADCMP600 19

4.4 回波信号分析 20

第五章 仿真与实验 21

5.1软件仿真 21

5.1.1 信号重构仿真 21

5.1.2降噪仿真 22

5.2实验结果 23

第六章 结论 25

致谢 26

参考文献 27

第一章 绪论

1.1研究背景以及意义

时域脉冲测量是当今一个非常重要的课题,在历史上,脉冲技术一直都被广泛运用在在电信和雷达领域中。其中通过脉冲技术的运用,空间雷达允许对目标位置和速度进行远处感知并测量定位其位置;闭路雷达和时域反射仪可以引导信号传输系统的远程探测。当今,计算机行业正在处于快速发展的时期。计算机的主要功能用途是快速处理信息,越来越快的时钟频率是大型集成电路运行的主要驱动力,对集成电路测试仪的脉冲波形测量能力同时也提出了越来越严格的要求。计算机工业中任何一个特定单元对这些测量作出反应的能力将是该单元的性能提高的一个日益增加的影响因素。其中一些知名的汽车公司中,都在自动驾驶等技术中广泛采用激光雷达等技术。通过发射激光光束来探测目标,并通过搜集反射回来的光束来形成点并获取数据,这些数据经光电处理后可生成为精确的三维立体图像。采用这项技术,可以准确的获取居有很高精度的物理空间环境信息,测距精度甚至已经可以达到了厘米级。这项技术同样是对超短脉冲的回波信号进行多脉冲合成的高精度重构从而进行数据处理以及分析。因此,超短脉冲测量在工业、雷达测距、电子示波器等诸多领域都有很高的运用价值。

时域脉冲测量是当今一个非常重要的课题,在历史上,脉冲技术一直都被广泛运用在在电信和雷达领域中。其中通过脉冲技术的运用,空间雷达允许对目标位置和速度进行远处感知并测量定位其位置;闭路雷达和时域反射仪可以引导信号传输系统的远程探测。当今,计算机行业正在处于快速发展的时期。计算机的主要功能用途是快速处理信息,越来越快的时钟频率是大型集成电路运行的主要驱动力,对集成电路测试仪的脉冲波形测量能力同时也提出了越来越严格的要求。计算机工业中任何一个特定单元对这些测量作出反应的能力将是该单元的性能提高的一个日益增加的影响因素。其中一些知名的汽车公司中,都在自动驾驶等技术中广泛采用激光雷达等技术。通过发射激光光束来探测目标,并通过搜集反射回来的光束来形成点并获取数据,这些数据经光电处理后可生成为精确的三维立体图像。采用这项技术,可以准确的获取居有很高精度的物理空间环境信息,测距精度甚至已经可以达到了厘米级。这项技术同样是对超短脉冲的回波信号进行多脉冲合成的高精度重构从而进行数据处理以及分析。因此,超短脉冲测量在工业、雷达测距、电子示波器等诸多领域都有很高的运用价值。

图1.1 自动驾驶中的车载激光雷达

超短脉冲信号的不失真采集和存储是提高回波重构精度和信噪比的前提,然而超短脉冲激光雷达的回波信号的脉宽往往只有几十纳秒的宽度。如果只用普通的低频ADC进行采集,那么回波的波型上只能采集到几个点。用这采集到的几个点是很难将激光雷达回波进行高精度重构的。因此,为了采样脉宽为几十纳秒的激光雷达回波,往往要用到采样频率很高的ADC。这种高速ADC不仅价格昂贵,而且具有一定的技术垄断。这种情况下,通过多脉冲合成的超短脉冲高精度回波重构技术可以实现低速的ADC来达到一个很高的等效的采样频率。这种方法可以大大的减少商品的技术成本以及打破国外对国内的高速ADC垄断。因此研究多脉冲合成的超短脉冲高精度回波重构技术有很大的现实意义以及实用价值。然而,使用多脉冲来高精度回波重构的方法,任何在采样过程中的其他信号的干扰都对重构的回波信号的精度造成影响,因此有必要来研究设计出避免这种误差的方法。随着各个领域对超短脉冲测量的需求逐渐增多,以及普通模拟-数字转换器的采样频率限制,运用多脉冲高精度重构超短脉冲信号的社会效益和经济效益无疑都是巨大的。

1.2 国内外研究现状

时域里面的实时脉冲测量一直是一个被广泛研究的学科。但是受制于普通模拟-数字转换器的采样频率在香浓采样定理下的限制,人们并不能轻易的对超短脉冲信号进行实时采集。在这样的情况下,国内外的学者就提出了用多脉冲合成的方法。这种方法一经推出,就被广泛用于数字示波器,视觉处理以及测距雷达系统等领域中。

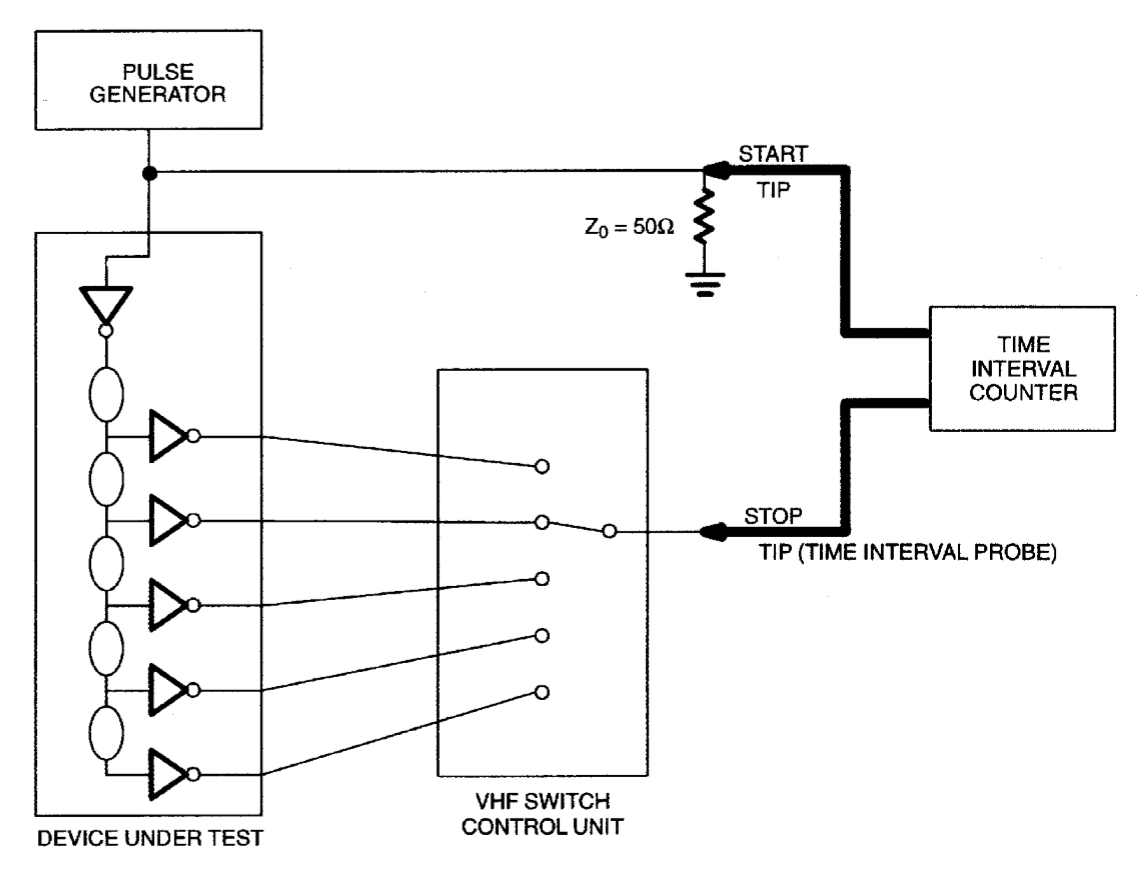

国外很多学者在多脉冲的超短脉冲合成上面以将有了许多的研究成果。Filomena M. C. Clemêncio等人在2007年在IEEE会议论文上提出了一种用交叉采样来获取高频信号的方法。该文中,其研究了交叉采样技术因为采集的信号不匹配可能导致不必要的谐波失真和噪声等影响被采样高频信号精度的因素。该方法用现有高速、250msps 8位A/D转换器采集通道通过交织的方法来对信号进行采样,并在文中的末端展示了相应的实验结果。其文中所提出的方法有相对较好的校准幅度。文中同时也提出了一种基于软件的动态幅度电平信号相关调整方法,该方法适用于频率宽带很宽的信号。在使用这种交织采样的等效采样的方法时可以大大提高采集信号的质量。所提出的技术即使在有噪声的情况下也能提供良好的结果[1]。 2017年的一篇IEEE会议论文中,有国外学者提出了一种可以扩展采集系统的带宽,实现对周期信号的高频采样的一种随机等效采样方法。该方法解决了随机等效采样的关键问题,即准确测量触发点与下一个采样时钟脉冲之间的时间间隔,并用时间对齐法确定采样数据在信号重构中的位置。其通过随机等效抽样的基本原理并基于双斜积分电路,提出了将双斜积分电路应用于5Gsps示波器的局限性,在此基础上设计了相应的等效采样系统,实现了200 Gsps的ADC等效采样,采样速率为5GHz。美国的著名示波器厂商Lecroy在其示波器Wavemaster中就加入了一个运用多脉冲合成超短脉冲的方法,来采集超短脉冲高频信号的功能,此功能利用高频信号的周期性,以牺牲更多时间为代价,采集超短脉冲各个周期不同的点来重构出一个完整的周期信号。

近年来国内也有很多学者从事脉冲高精度重构技术以及相关领域的研究。武汉的华中科技大学电子与信息工程学院的黄健学者,在2002年华中科技大学学报上介绍了一种用低速A/D转换器构成的采样系统来采样高频宽带信号的高速顺序采样的方法。在该方法中,其根据FPGA中的锁相环设计和触发的原理,设计出了差频采样的原理框图以及触发电路,该方法有别于传统的顺序采样,解决了顺序采样过程中可能的抖动所会带来的采样精度等问题,提高了顺序采样所采样的点用来还原被采样波形的波形精度[2]。中国科技大学近代物理系的王硕方等学者在2002年将开放的模块化仪器标准总线系统VXI和等效采样相结合设计出了一种数字存储示波器。用40MB的采样频率可以对10G的被采样信号进行采样[3]。 国防科技大学的陆珉学者曾在2005年在测量技术刊物发表了一篇论文上阐述了如何实现用等效采样模块来对高频回波信号回波信号的采集,其阐述的采样系统可以将等效的采样频率达到20Gsps。其文中同时分析了对该采样系统可能造成的各种干扰,提出了如何减少这些干扰的若干种措施[4]。北京理工大学的机械与车辆学院的冉学均学者2010年曾在第二十九届中国控制会议发表过一篇论文,其中阐述了一种激光雷达全波采样的高宽带数据采样系统。文中,该系统通过4个型号为AD9840、采样频率为250M的A/D转换芯片,利用时钟芯片AD9520-3来对这四路A/D转换芯片进行时序和相位控制,使每个A/D转换芯片之间的相位都相差90度,然后通过以FPGA控制A/D转换器进行数据的采集,拼接与传输,最终效果可以通过4片采样频率为250M的A/D转换器采样频率为1G的雷达信号,这种方法可以可以适用在激光雷达的高频信号采样上,解决的长期以来在激光雷达信号采集中受到低速A/D转换器局限的问题[5]。武汉的华中科技大学的控制科学与工程学院的张杰学者在2011年提出了基于游标法的等效时间采样模块的设计,其中采样步长越小那么等效时间采样模块的采样精度也就越大,该系统有效实现了高速脉冲的数据采集。这种思路设计的模块也同时具有成本低、精度高、易于实现的特点, 可以运用在TDR的测量系统设计中[6]。

1.3 课题研究内容

此毕业设计主要研究多脉冲合成的超短脉冲高精度回波重构技术。其核心步骤为用verilog硬件设计语言在FPGA中利用其内置的时钟信号调制一个满足调制需求的周期发射脉冲。发射脉冲信号并产生超短脉冲的回波信号后,通过FPGA,低频模拟-数字转换模块对被采样信号进行采样。模拟-数字转换模块在超短脉冲回波信号中的多个周期信号中进行信号的采集,然后再用这些采集到的点进行脉冲信号的重构,高度还原出超短脉冲的一个具有周期性的波形。

本课题的主要研究内容如下:

1)分析短脉冲采样的基本难题;

2)研究发射脉冲调制时序与重构算法;

3)研究回波降噪的基本方法;

由于在信号的传播工程中,会有很多的噪声信号进行干扰,其中主要的噪声源为白噪声,这些干扰会对重构的超短脉冲波形的精度造成影响。于是在此毕业设计中,拟在通过数据累加的方法来减少这种噪声的干扰,来提升重构超短脉冲波形的精度和准确性。

第二章 多脉冲合成的超短脉冲高精度回波重构方法研究

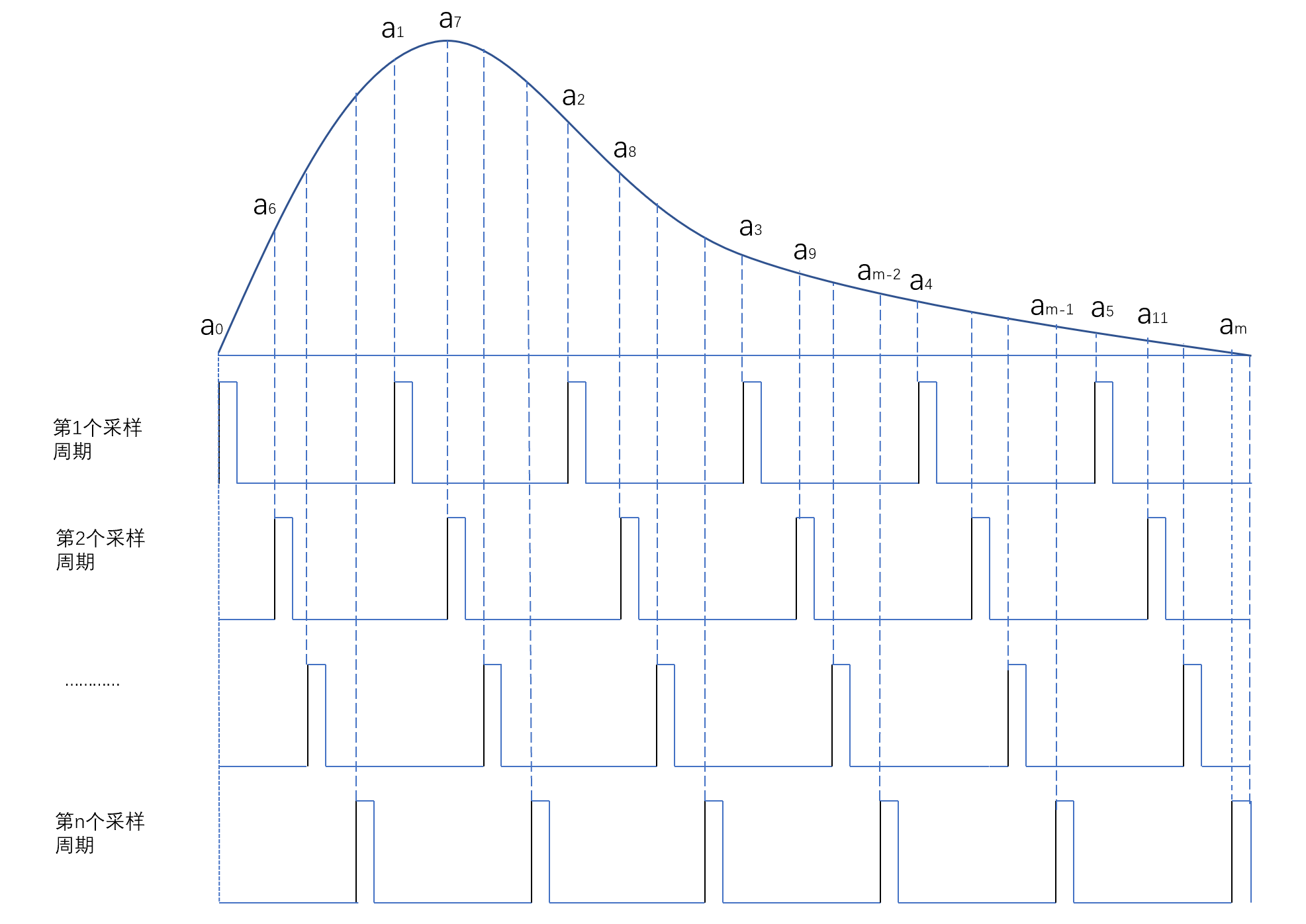

多脉冲合成的超短脉冲高精度回波重构技术中最常见的方法就是等效采样法,如数字示波器核心技术之一就是等效采样。相比实时采样,等效采样技术可以大大提高等效采样率,减缓了硬件实时采样率及数据存储速率和存储容量的压力。这种方法可以使低速的A/D转换器采样那些频率超过香浓采样定理所规定的信号。等效采样法相比于传统的采样方法,其往往以牺牲更多的采样时间为代价,来获取周期信号在一个周期内尽可能多的采样点,已达到后期可以高精度还原被采样信号的目的。等效采样法主要分为两类,分别是顺序采样法以及交错采样法[7]。

2.1 顺序采样法

2.1.1 顺序采样原理

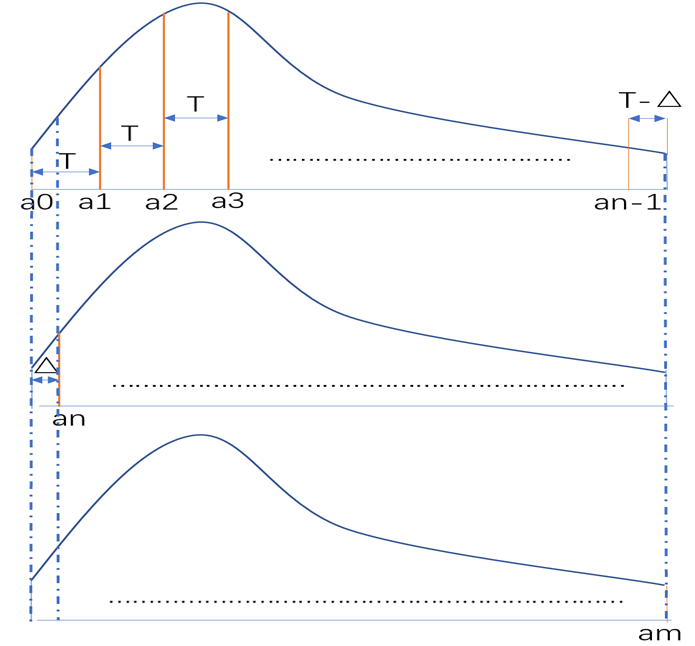

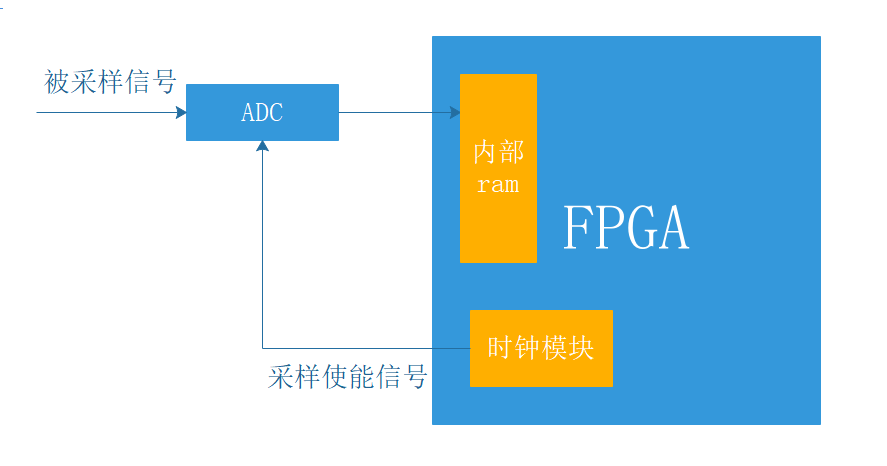

顺序采样结构图如图2.1所示。顺序采样中,当第一个上升沿跳变触发脉冲到来时,ADC对被采样信号进行采样,并将采样到的采集点存入到FPGA中。当ADC的第二个触发脉冲到来时,ADC对被采样信号进行采样,并同样的储存在FPGA中。以此类推,当ADC对被采样信号采集完信号上所有点后,用ADC采集的信号点可以重构出被采集信号[6, 8]。

顺序采样结构图如图2.1所示。顺序采样中,当第一个上升沿跳变触发脉冲到来时,ADC对被采样信号进行采样,并将采样到的采集点存入到FPGA中。当ADC的第二个触发脉冲到来时,ADC对被采样信号进行采样,并同样的储存在FPGA中。以此类推,当ADC对被采样信号采集完信号上所有点后,用ADC采集的信号点可以重构出被采集信号[6, 8]。

图2.1 顺序采样结构图

2.1.2 顺序采样具体步骤

通过FPGA实现顺序采样的具体步骤如下:

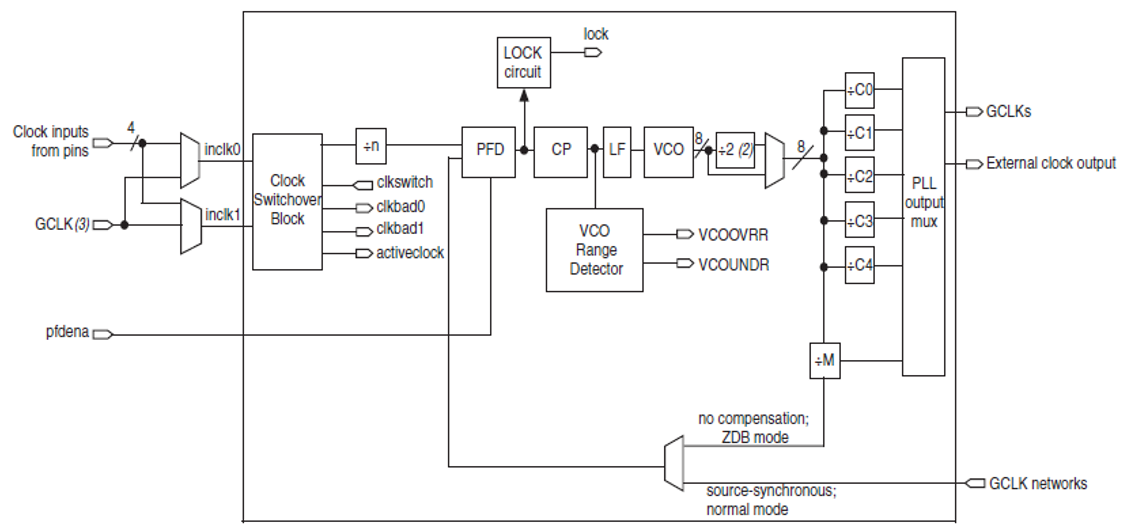

步骤一:通过FPGA的锁相环LLP将FPGA中内置的时钟信号分为相角差各位90度的四路时钟信号,这样四路时钟信号产生一个很小的△以得到一个很高的精度。

步骤二:通过FPGA给A/D转换器一个控制信号,A/D转换器在控制信号的控制下进行采样,采样所得到的信号储存在FPGA中。

步骤三:将这些采样所得到的采样点按照采样顺序进行排序, 然后将采样所得到的采样点按照特定顺序排序,对被采样信号进行重构。

2.2 交错采样法

2.2.1 交错采样原理

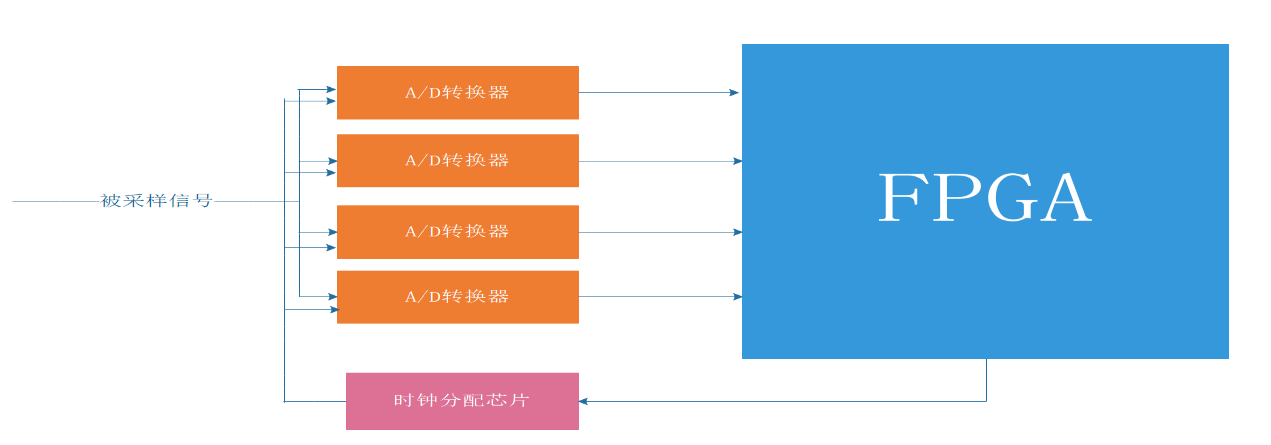

多ADC交错采样即是用多个ADC通过时钟芯片的控制的控制,使每个A/D转换器之间的相位角造成有90度的偏差。然后FPGA给每个A/D转换器轮流的发送一个采样信号进行采样。这种情况下,一个ADC在采样了之后,另一个ADC则可以在第一个ADC采样完成之后,通过FPGA控制的方波触发之后进行采样,这样一来,多个相同的采样频率的ADC就可以采样超过采样定理所规定的高频信号。如过,有四个采样频率为250M的采样信号,那么就可以在交错采样定理下采样频率可以达到1G。[9]

多ADC交错采样即是用多个ADC通过时钟芯片的控制的控制,使每个A/D转换器之间的相位角造成有90度的偏差。然后FPGA给每个A/D转换器轮流的发送一个采样信号进行采样。这种情况下,一个ADC在采样了之后,另一个ADC则可以在第一个ADC采样完成之后,通过FPGA控制的方波触发之后进行采样,这样一来,多个相同的采样频率的ADC就可以采样超过采样定理所规定的高频信号。如过,有四个采样频率为250M的采样信号,那么就可以在交错采样定理下采样频率可以达到1G。[9]

图2.2 交错采样结构图

2.2.2 交错采样具体步骤

通过FPGA实现交错采样的具体步骤如下:

步骤一:FPGA通过内部的时钟提供时钟芯片一个给定频率,时钟芯片根据FPGA提供的给定频率产生四路相位相差90度的时钟信号。

步骤二:四个A/D转换器芯片根据时钟芯片根据时钟芯片分配的时钟信号,对被采样信号进行采样。FPGA将被采样的信号点存入FPGA中。

步骤三:将这些采样所得到的采样点进行排序,然后将采样所得到的采样点按照特定顺序排序,对被采样信号进行重构。

2.3 顺序采样方法和交错采样方法比较

我们从以上的结论中可以看出,顺序采样因为其往往只有一个A/D转换器在采样,并需要被采样信号的很多个周期中,所以其采样时间往往要大于交错采样。然而,由于其采样电路中只包含一个A/D转换器,所以他的成本比交错采样电路所需要多个A/D转换器的成本要低很多。并且顺序采样并不需要额外的外围电路,如时钟分配器。所以其实现起来简单,并且采样系统相对稳定。

交错采样往往需要多个的A/D转换器之间的配合,并且配合起来必须十分的严密,如果硬件电路有一点点的不稳定和误差,就会导致A/D转换器之间的采样存在误差,所以其对硬件电路的要求特别的高。第一个误差是现有的时间分配器在现有的计数条件下很难达到很高的精度,那么造成的后果就是每个A/D转换电路之间的采样是非均匀的。着就会对采样系统采样精度造成很大的干扰。因为交错采样的核心原件之一就是时钟分配器。第二个误差来源于不同的A/D转换器往往具有不同的采样延迟,所以这也会导致采样的不均匀,导致所采样点之间的相位角之间往往不是90度,所以导致采样精度降低。[10]

在后面的章节中,我将对顺序采样进行仿真以及实验。

2.4 增强信噪比SNR的方法

有时候处理的信号强度非常的弱,所以我们往往需要一定的手段来提高信号的信噪比。众所周知,对被采样信号干扰的信号最多的往往是高斯白噪声,高斯白噪声的瞬时值服从高斯分布,而它的功率谱密度又是均匀分布的。其中高斯白噪声的中值为0,方差我们记作σ2,因为它服从正态分布,所以我们可以记为X~N(u,σ2), 高斯分布的一维概率密度可表示为式:

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示: