高速串行通信系统均衡器的仿真设计毕业论文

2020-02-17 22:21:29

摘 要

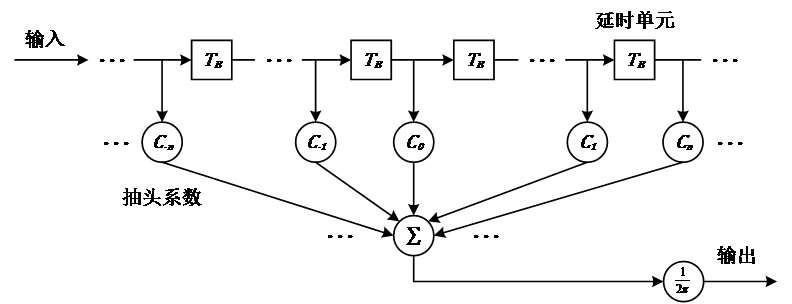

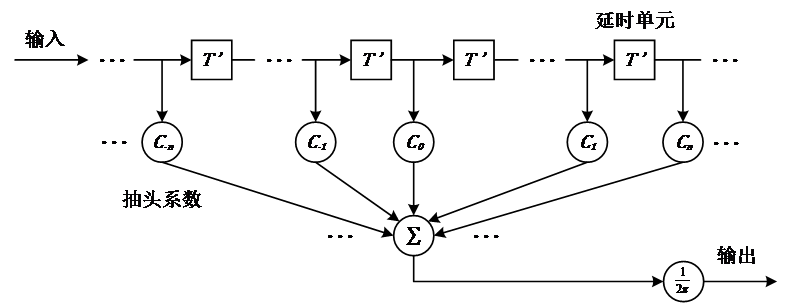

本文第1章至第3章串行通信链路中的时域均衡器进行了分析研究。在第1章交代了研究背景与现阶段国内外研究现状。第2章首先为了方便后续分析建立了数字基带传输系统模型,然后针对模型中信道的非理想特性进行了定性分析,最后对由于信道的非理想特性而产生的符号间干扰进行了定量分析。第3章则在第2章最后对符号间干扰定量分析的基础上导出了消除符号间干扰的频域条件和时域条件,并根据频域条件导出了时域均衡器的结构。至此均衡器对符号间干扰的作用原理已交代完毕。第3章剩余部分交代了两种常用的时域均衡器抽头系数的计算方法,并介绍了具有更强鲁棒性的分数间隔均衡器。

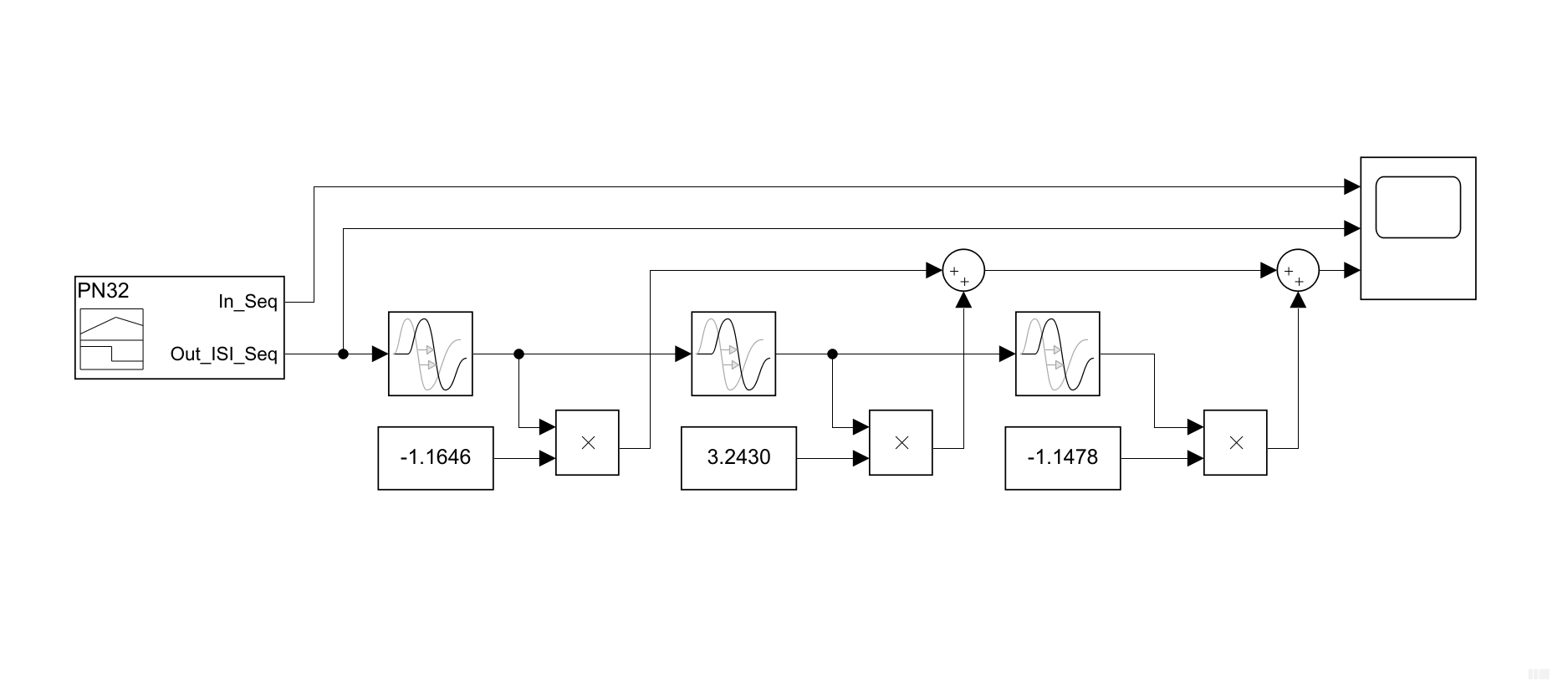

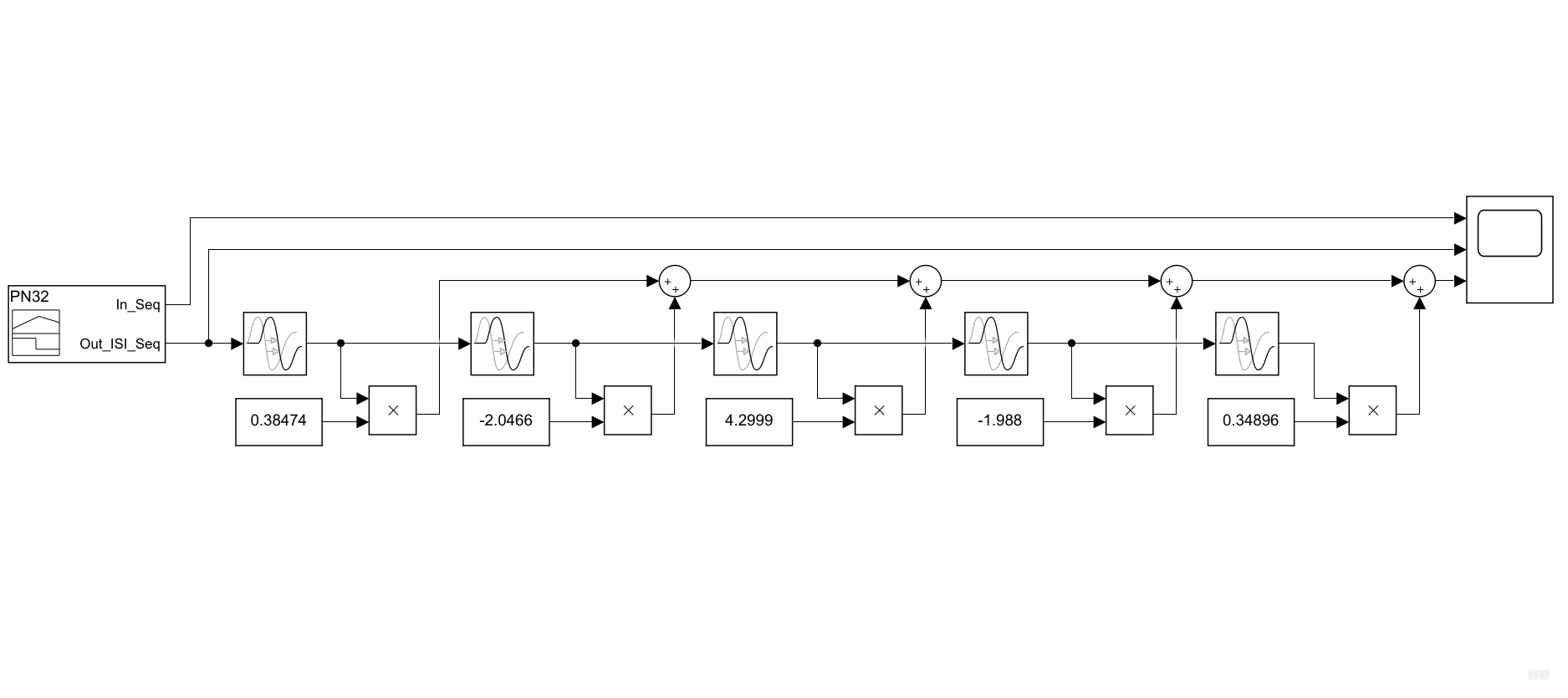

文章第4章使用理想运算单元搭建了一个3抽头分数间隔均衡器,并使用Virtuoso与Simulink对均衡器的均衡效果进行了仿真,最后分析了仿真结果。第5章使用实际电路实现了第4章中搭建的3抽头分数间隔均衡器,并在Virtuoso中对均衡器均衡效果进行了仿真,并分析了仿真结果。

关键词:数字通信;均衡器;分数间隔均衡器;最小均方算法;横向滤波器

Abstract

The transversal filter used in serial communication link is analyzed in chapter 1 to chapter 3. In chapter 1, the research background and current research situation at home and abroad are introduced. In chapter 2, the digital baseband transmission system model is established for the convenience of subsequent analysis. Then, the non-ideal characteristics of the channel in the digital baseband transmission system model are qualitatively analyzed. Finally, the inter-symbol interference caused by the non-ideal characteristics of the channel is quantitatively analyzed. In chapter 3, on the basis of the quantitative analysis of the inter-symbol interference in chapter 2, the constraints of eliminating the inter-symbol interference are derived in frequency-domain and time-domain, and the structure of the transversal filter is derived according to the frequency-domain constraints. From now, the reason why the transversal filter can reduce the inter-symbol interference has been explained. The remaining part of chapter 3 introduces two kinds of calculation methods of tap coefficients of the transversal filter and introduces the fractionally-spaced equalizer (FSE) which is more robust.

In chapter 4, a 3 tap FSE is built with the ideal computing unit, and the equalization results of the equalizer is simulated with Virtuoso and Simulink. Finally, the simulation results are analyzed. The 3 tap FSE built in chapter 4 is built by circuits in chapter 5. The equalization results of the equalizer are simulated in Virtuoso and the simulation results are analyzed.

Key Words: digital communications; equalizer; FSE; LMS; the transversal filter

目录

摘要 I

Abstract II

第1章 绪论 1

1.1 研究背景 1

1.2 国内外研究现状分析 1

1.3 研究的主要内容与论文结构安排 2

第2章 数字基带信号传输系统信道建模 3

2.1 数字基带信号传输系统模型 3

2.2 信道的非理想特性 3

2.3 符号间干扰的产生 5

第3章 基带通信系统信道时域均衡原理 9

3.1 无符号间干扰条件 9

3.2 时域均衡原理 11

3.3 抽头系数的计算 15

3.3.1 迫零法 15

3.3.2 最小均方误差法 17

3.4 分数间隔均衡器 19

第4章 基于理想运算单元的分数间隔均衡器仿真实现 21

4.1 仿真的思路与方法 21

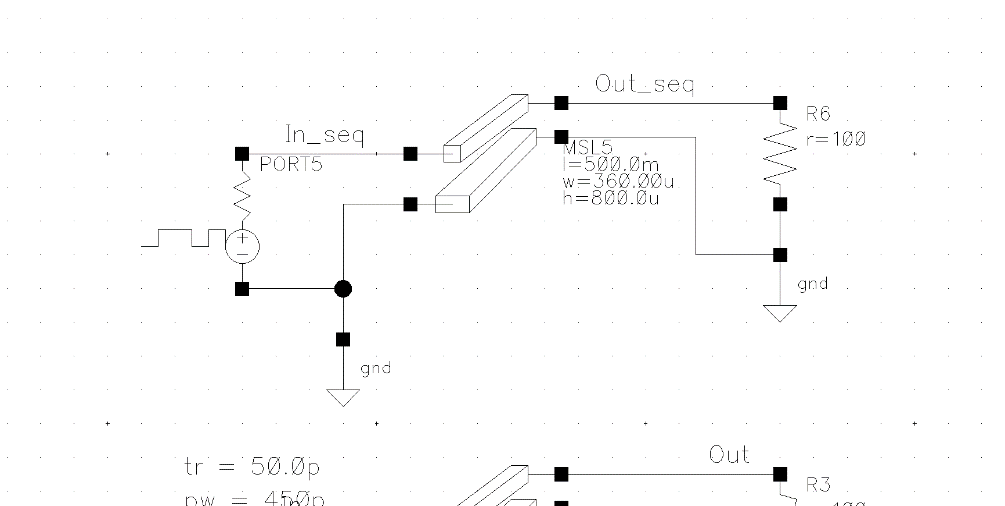

4.2 仿真拓扑搭建 21

4.3 仿真结果 23

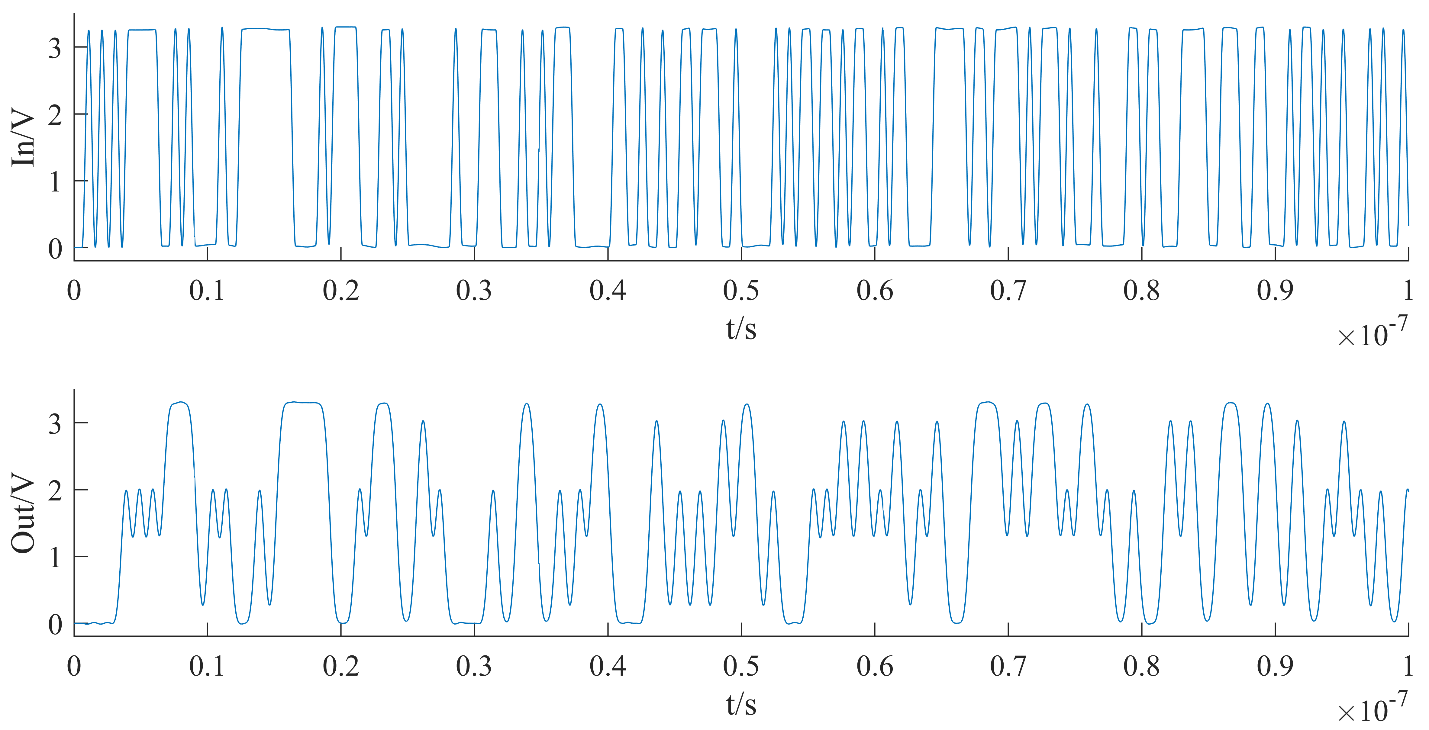

4.3.1 信道输入信号与信道输出信号 23

4.3.2 分数间隔均衡器均衡结果 25

第5章 分数间隔均衡器的电路实现 27

5.1 延时线电路 27

5.1.1 延时电路原理分析 27

5.1.2 延时线电路搭建与仿真结果 30

5.2 乘法器 31

5.2.1 原理分析 32

5.2.2 参数设计准则 35

5.3 乘加电路 38

5.3.1 原理分析 38

5.3.2 实际电路搭建与仿真结果 41

5.4 分数间隔均衡器的电路搭建与均衡结果 43

第6章 总结与展望 45

参考文献 46

致谢 48

绪论

本章交代了本文的研究背景,交代了所研究内容现阶段国内外分析现状,最后叙述了文章总体的结构安排。

研究背景

现今人们对数据传输速率的要求日益增加已经成为不争的事实。而由于传统的并行数据传输存在着串扰、偏差及抖动的问题,而且并行传输需要准确的同步时钟信号或握手信号,当数据速率提高时,意味着时钟速率也会提高,就可能引起数据传送的时序和时钟难以合拍,从而造成数据信号接收错误,并且时钟速率的提高也会引起信号线间的干扰以及时钟偏斜,从而导致传输错误,因而并行传输很难实现高速传输[1]。另外,并行传输方式需要占用很多的传输媒介,这使得并行传输的板级布线非常为复杂,同时也大大提高了单板的生产制造成本[2]。

与并行传输方式相比较,高速串行通信最少仅需占用2根数据线便能完成数据的传输,极大地节约了传输媒介,降低了系统互联的复杂性,有利于单板制造成本的降低。同时,串行数据传输是可以是异步传输,无需像并行数据传输那样需要传输非常严格的时钟同步信号,因此能以非常高的速率在信道中传输[1]。另外,串行数据传输还较并行数据传输拥有更低的功耗[3]。正因为串行传输有如此之多的优点,现在其已经成为主流的数据传输方式,在片上dice间通信[4]、单板芯片间高速互连通信[4]、有线通信、背板通信以及高速接口领域得到了广泛应用。

然而对于高速串行传输,由于信道非理想特性引起的符号间干扰是影响数据速率提高的关键因素。而利用均衡技术能够补偿由于信道非理想而带来的传输信号失真,这使得均衡技术成为高速串行数据传输系统中关键部分。因此,均衡技术的研究具有重要的应用价值。

国内外研究现状分析

由于串行传输技术的应用越来越广泛,数据速率越来越高,对其技术的研究也引起了学术界和工业界的广泛关注。

意大利帕维亚大学在2018年基于28 nm CMOS工艺设计了一种用于背板通信的25Gb/s的2进制码均衡器[5]。韩国科学技术院在2018年基于40 nm CMOS工艺设计了一款用于FPWM均衡的20 Gb/s速率均衡器[6]。2018年Rambus公司使用14 nm FinFET工艺设计了一种4通道、每通道1.25~28.05 Gb/s收发速率的2进制码串行收发机[7]。中国电子科技集团有限公司在2018年对传输速率达100 Gb/s的双二进制码传输系统的均衡进行了信道实测和仿真研究[8]。2019年NVIDIA公司基于16 nm FinFET工艺设计出了一种用于芯片封装内部dice间互联或极近封装间互联的25 Gb/s的2进制单端串行链路均衡器[4]。德克萨斯Aamp;M大学在2018年基于65 nm CMOS工艺设计了56 Gb/s用于PAM4接收机的均衡器[9]。Intel公司在2018年对传输速率超过112 Gb/s的PAM4系统均衡理论及方案进行了研究[10]。

研究的主要内容与论文结构安排

本文对时域均衡器的均衡原理进行了详细的演算分析,并使用实际电路实现了一个分数间隔均衡器。

第一章,介绍了均衡器的诞生背景,介绍了现阶段均衡器国内外的研究现状。

第二章,为后续分析建立了数字基带信号传输系统的模型,分析了数字基带信号为何会存在符号间干扰,定量地表述了符号间干扰的产生。

第三章,确定了信号无符号间干扰的时域条件与频域条件,根据信号无符号间干扰的频域条件导出了时域均衡器的实现结构,介绍了两种时域均衡器抽头系数的计算方法,分析了波特间隔均衡器的不足,分析了分数间隔均衡器对延时单元延时误差不敏感的原因。

第四章,介绍了使用理想运算单元实现分数间隔均衡器的思路和具体仿真方法,展示了信道两端信号的仿真结果,展示了均衡器均衡效果的仿真结果。

第五章,介绍了运算单元的电路实现,搭建了微间隔均衡器的实际电路,展示了微间隔均衡器实际电路的仿真结果。

第六章,对全文进行简单总结,分析现有不足,对未来工作进行了展望。

数字基带信号传输系统信道建模

本章为了后续讨论的方便,首先建立了数字基带信号传输系统的模型,而后分析了数字基带信号传输系统模型中信道部分的不良特性对数字基带信号传输带来的不利影响,最后对这种影响进行了定量的分析讨论。

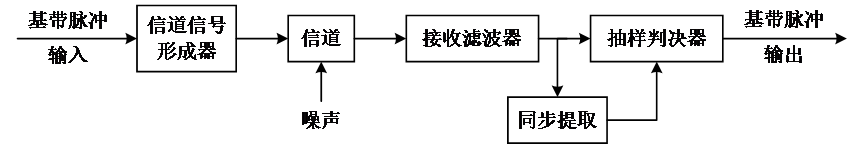

数字基带信号传输系统模型

一个典型的数字基带信号传输系统如图2.1所示。数字基带信号传输系统一般包括信道形成器、信道、接收滤波器、同步提取以及抽样判决器等功能单元。图2.1中的基带脉冲输入一般是通信发送端经码型变换后产生的携带有用信息的信道传输码,而基带脉冲输出则为经抽样判决器还原出来的将要送至通信接收端还未经码型变换的携带有用信息的信道传输码。

图2.1 典型的基带通信系统

信道信号形成器的功能是产生合适于信道传输的基带信号波形。因为基带脉冲输入一般为边沿跳变速度很快的矩形脉冲,其所占带宽很宽,不适合在信道中直接传输。信道信号形成器就是用于压缩这种不适于信道传输波形的频带,将其变换成为占用有限带宽的适合在信道当中传播的基带信号波形。

信道则为基带信号传输的介质,通常为诸如微带线、双绞线、同轴电缆等的有线信道。信号经过信道会叠加上噪声,另外由于信道的非理想特性,信号经过信道后亦将发生畸变。有关信道的非理想特性导致的信号畸变将在2.2节与2.3节中详细讨论。

接收滤波器的功能是尽量补偿信道的非理想传输特性,并尽可能滤除信道噪声。显然,本文研究的均衡器属于接收滤波器部分。

抽样判决器则是在规定时刻对接收滤波器的输出波形进行抽样判决,以恢复或再生携带有用信息的信道传输码。

同步提取的功能则是从接收滤波器输出信号中为抽样判决器提供位定时脉冲,位定时的准确与否将直接影响判决效果。

信道的非理想特性

导致数字基带信号传输信道非理想的第一个因素是电压反射的存在。数字基带信号传输一般以导线作为传输信道,而当数字基带信号传输速率加快时,则需要对这一“导线”提出一些更加严苛的要求。数字基带信号传输速率的提高必然伴随着信号边沿跳变沿速度的加快,拥有陡峭上升/下降沿的高速数字信号在传输时需要保证其所在传输线上沿线所感受到的瞬时阻抗保持恒定,否则被传输的信号可能会在信号跳变沿到达一些阻抗不连续的点时发生反射从而使被传输信号发生畸变,导致接收端对信号产生误触发从而增导致系统传输误码率的增加。对于印刷电路板来说,信号在传输线沿线上感受到的瞬时阻抗同当前位置信号线印刷宽度、信号线本身厚度、信号线同回流路径间的介质厚度、介质本身的特性以及信号传输沿线回流路径的完整性有关[11]。因此,为了避免上述问题的产生,高速串行链路间的互连一般使用均匀传输线实现。

但是,信号反射的存在并非是导致信道非理想的唯一因素。即便可以通过设计,将传输线沿线的瞬时阻抗严格控制为同一值,并且在源端负载端都做好了完美的匹配,信号反射被完全消除,此时的信道依旧不能称作理想信道。因为还有另一因素会使得被传输数字信号产生畸变,这一因素就是传输线传输损耗的频率相关性。

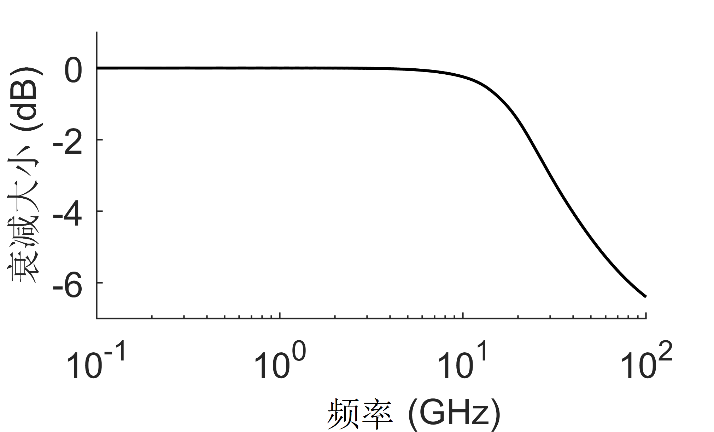

信号沿传输线传播时,由于存在导线损耗和介质损耗[11],最终到达接收端的信号,其幅度会相较于发送端发生衰减。倘若这种衰减对被传输信号每一频率分量的衰减大小都相同,那么在接收端对接收信号做信号带宽内的放大即可补偿这种衰减。可问题就在于,由于趋肤效应以及介质损耗的频率相关性,实际传输线对经过其信号的高频分量的衰减要大于对其低频分量的衰减。图2.2为一实际传输线对不同频率分量的衰减大小仿真结果,从结果中可以看到,小于10 GHz的频率分量经过此传输线几乎不会发生衰减,而高于12 GHz的频率分量经过此传输线则会产生较为显著的衰减,并且衰减量的大小会随着信号分量频率的增加而增大。

图2.2 实际传输线对不同频率分量的衰减大小仿真结果

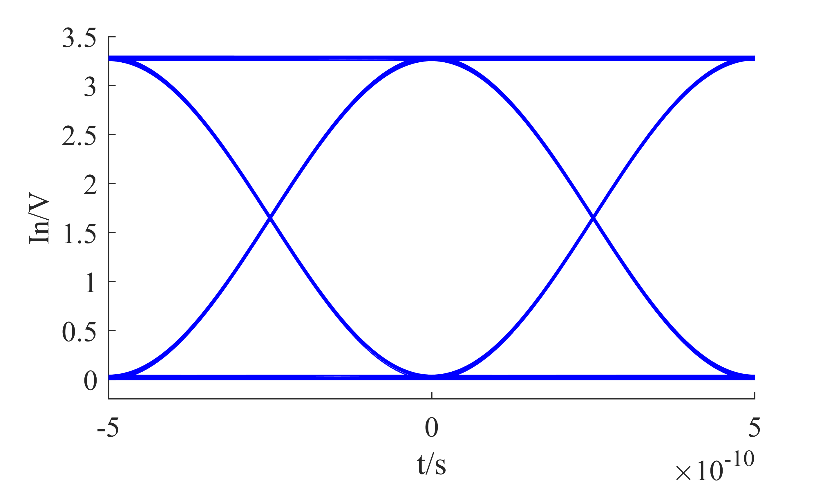

传输线传输损耗的频率相关性导致的信道非理想会给数字基带信号传输带来许多问题,其中对设计者来说最严峻的挑战是其带来的符号间干扰。有关信道非理想而带来符号间干扰的详细分析与定量描述将在2.3节中叙述。

符号间干扰的产生

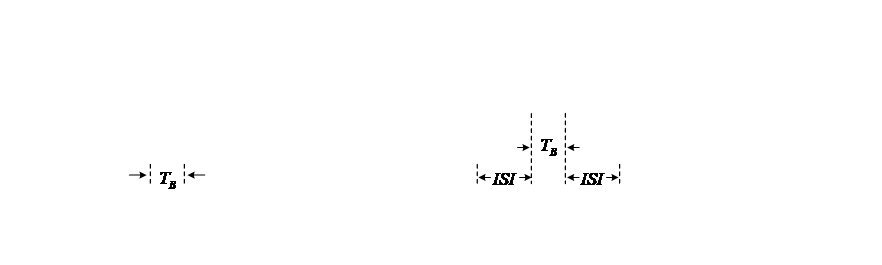

从2.2节的讨论我们知道,由于传输线传输损耗的频率相关性,信号经过传输线后其高频分量会被部分衰减。这一特性反映在时域上的表现为:实际传输线在匹配良好的情况下,除了像理无耗输线那样会给被传输信号带来延时以外,还会平滑信号快速变化的部分,这对高速数字信号来说就将会拉长信号的跳变,从而使得单个码元信号发生延展,占用多个码元周期的时间。而超过本码元持续时间的那一部分向两端的延展会干扰后续或先前码元的判决,这就是符号间干扰产生的根本原因。如图2.3所示。

图2.3 单个码元信号发生延展产生符号间干扰

为了找出应对ISI的方法,我们首先要对信道以及所传输的信号进行建模,而后利用数学工具分析信号经过信道后会产生怎样的行为,得到符号间干扰的数学描述,再进一步商讨对策。

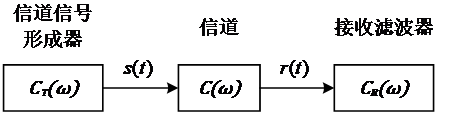

由图2.1我们可以知道,与信道直接对接的单元为信道信号形成器与接收滤波器。信道信号形成器的输出信号直接被送至信道上传输,在信道的另一端,经过信道传输的信号则作为接收滤波器的输入信号被送入接收滤波器进行均衡与去噪。为了对符号间干扰的产生进行定量分析,我们设信道信号形成器的输出信号为,信道频率响应为,接收滤波器输入信号为。则上述过程可抽象为图2.4所示的数学模型。与分别为信道信号形成器与接收滤波器的频率响应。

图2.4 信道传输的数学模型

信道信号形成器的输出信号可以表示成

(2.1) |

式(2.1)中为任意整数,表示输入信道信号形成器的离散符号序列。表征由信道信号形成器产生的单个脉冲波形,其拥有有限的带宽,因而适宜在信道上传输。与中单个元素的乘积可在连续时域上表征一个信息符号。

式(2.1)的物理意义为:对做整数倍的位移,再将位移后的与序号同位移周期倍数相同的元素相乘,再将所有相乘结果求和,得到表达式即为信道信号形成器输出信号的连续时域表达式。

设为信道频率响应的傅里叶逆变换,即

(2.2) |

则经过信道后,波形变为,与的关系为

(2.3) |

其中为卷积计算。将式(2.1)带入式(2.3)得

(2.4) |

根据卷积计算的分配律性质有

(2.5) |

再根据卷积计算的定义有

(2.6) |

为了分析符号间干扰的产生,我们希望将式(2.6)中的拥有同式(2.1)中的相同的形式,以便以码元持续时间为周期分析码元之间互相存在的影响。为此,我们需要对式(2.6)中的卷积积分部分做形式上的转换。设

(2.7) |

则式(2.6)可写为

(2.8) |

对式(2.7)等式右边做积分变量代换,令,并注意到:,当时,当时,因而有

(2.9) |

整理式(2.9)得

(2.10) |

将积分变量替换回常用积分变量得

(2.11) |

注意到式(2.11)等式右边可看作变量为的函数,设此函数为,即有

(2.12) |

将式(2.12)代入式(2.11)得

(2.13) |

再将式(2.13)代回式(2.8),得到

(2.14) |

对照式(2.1)与式(2.14)可以看到,此时与具有相同的形式。结合由式(2.2)至式(2.13)的分析过程,我们可以很清晰地得到与的物理意义:表示在单个输入脉冲的作用下,经由形成的单个输出脉冲波形;而则表示在位移n个码元周期的单个脉冲的作用下,形成的输出波形。

结合上述分析,我们可以得出式(2.14)所表征的物理意义:将(即在位移n个码元周期的单个脉冲的作用下,形成的输出波形)与序号同位移周期倍数相同的元素相乘,再将所有相乘结果求和,得到表达式即为经过信道后的信号的连续时域表达式。

以上是毕业论文大纲或资料介绍,该课题完整毕业论文、开题报告、任务书、程序设计、图纸设计等资料请添加微信获取,微信号:bysjorg。

相关图片展示: