基于FPGA的多标准可配置FSK解调器外文翻译资料

2022-12-10 16:01:43

英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

基于FPGA的多标准可配置FSK解调器

Haytham Azmi, Hamed Elsimary, M. Ibrahim Youssef, Ahmad Safwat

Electronics Research Institute, ME, EL-Tahrir St., Dokki, Cairo 11361, Egypt

AL-Azhar University, Cairo, Egypt

Received 19 April 2003; accepted 20 August 2003

摘要:本文介绍了基于FPGA的可配置的FSK解调器的设计与实现,它可以支持多标准,如被介绍的ITU-T V.23和BELL 202。为了检测 FSK符号, 采用了一种新颖的数字信号处理算法。FSK 检测器的设计是可配置的,它可以在运行时切换不同的标准。通过使用该算法, 解调器可以配置为用于表达 FSK 符号的任何频率。

这可以通过增强的误码率相对于其他使用的数字算法进行。讨论了实现算法与所用技术之间的匹配问题。我们的目标技术是Altera 和 Xilinx 的芯片,以指导任何设计师想要在他的设计中使用这一技术。

关键词:FPGA;解调;DSP;FSK-BELL202;ITU-T V.23;1200-baud rate

1 介绍

对基于现场可编程门阵列 (FPGA) 的重构算法的实现进行了大量的研究。FPGA 是在设计器完全控制下的逻辑单元或模块和互连线的正规结构。作为数字信号处理 (DSP) 系统和数字通信应用的设计者, 我们有大量的选择来实现我们的解决方案。每个解决方案都有其优缺点。由于栅阵列向 DSP 设计器提供的并发程度较高, 因此在这里批准了使用 FPGA 技术实现 DSP 系统作为数字通信解决方案的选择。栅极阵列是一个自定义芯片,它允许构造非常具体的数字电路实现。我们的研究领域是实现自动调制识别(ARM)采用FPGA技术的算法。本文介绍了这项研究的第一步,即二进制频移键控 (BFSK) 解调器的设计与实现。同时提出了一种新颖的盲检测算法。也就是说,检测器没有关于传入 BFSK 的输入符号频率或比特率的信息。当然, 没有无限的波段检测器, 但设计者可以将检测器配置为估计的目标波段。这些接收器的应用通常是军事的。通过 Altera 和 Xilinx 的实例,提出了不同目标技术的实现比较。第二节介绍了对 FSK应用和解调过程中使用的技术的简短调查。对DSP技术进行了改进,以适应 FPGA技术的实现, 使其相对于其他技术得到更好的误码率,并在第三节中突出显示时钟恢复电路。这项工作是通过在工业应用中已经使用的两个标准的例子的:BELL202和ITU-T V.23,在EST 300的原型下提出的。在第三节中我们讨论了如何使这个设计能够配置,这样它就可以作为一个参数化检测器的许多标准。通过本文,我们强调了设计和实现问题以及如何克服这些问题。第四节对FPGA技术的选择进行了讨论,并在第五节给出了区域和时延的优化结果,设计使用VHDL语言描述所有解调模块。

2 FSK解调器概述

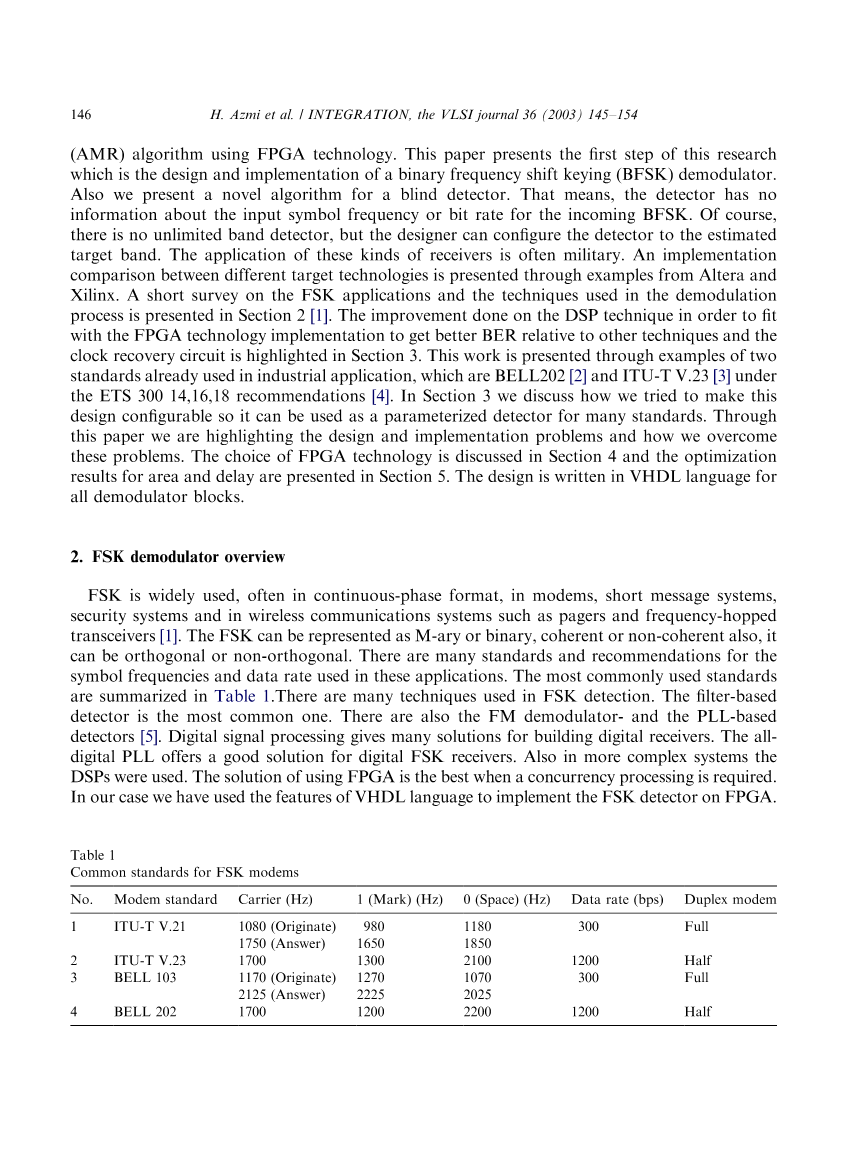

FSK在调制解调器、短消息系统、安全系统和无线通信系统 (如寻呼机和跳频收发器) 中广泛使用,通常是连续相位格式。FSK也可以表示为 m 元或二进制,相干或非相干,它可以是正交或非正交。在这些应用程序中使用的符号频率和数据速率有许多标准和建议。最常用的标准概括在表1。有很多技术应用在FSK检测中。filter-based 检测器是最常见的检测器,还有调频解调器和基于锁相环的检测器。数字信号处理为数字接收机的建设提供了许多解决方案。全数字锁相环为数字FSK接收机提供了良好的解决方案。并且在更加复杂的系统DSP使用了。在需要并发处理时, 使用 FPGA的解决方案是最好的。在本例中,我们利用 VHDL语言的特点,在 FPGA上实现了FSK信号检测器。

|

No.1 |

调制解调器标准 |

载波(Hz) |

1(Hz) |

0(Hz) |

信息率 |

双工调制解调 |

|

1 |

ITU-T V.21 |

1080(产生) |

980 |

1180 |

300 |

Full |

|

1750(回应) |

1650 |

1850 |

||||

|

2 |

ITU-T V.23 |

1700 |

1300 |

2100 |

1200 |

Half |

|

3 |

BELL 103 |

1170(产生) |

1270 |

1070 |

300 |

Full |

|

2125(回应) |

2225 |

2025 |

||||

|

4 |

BELL 202 |

1700 |

1200 |

2300 |

1200 |

Half |

表1 FSK调制解调器通用标准

我们的FPGA内部功能图包含模式选择器、同步器、综合器、判决设备和时钟恢复。模式选择器用于在运行时选择两个标准。同步器用于与系统主时钟同步所有系统信号。对于集成, 我们没有使用常规的集成概念。我们已经开发了常规的基于DSP的积分器, 以增加在符号之间的码元。然后, 判决设备输出对应于接收信号的二进制数据。时钟恢复电路用于将接收器符号持续时间发生器与传输信号同步。在下一小节中, 我们将介绍这个解调器的每个模块的细节。

3 BFSK解调器的设计与实现

DSP-based 检测器使用了积分极值的区别, 以区分lsquo;0rsquo;和lsquo;1rsquo;。图1(b)描述了这个方法的概念。该判决装置减去最大值减去最小值, 以提供足够高的噪音边缘。这是在符号频率太接近且没有像我们的标准情况那样正交时使用的最好的FSK检测方法。事实上, 我们在实施中有两个问题。第一个是在 BELL202 中使用的频率, 或在ITU-T V.23中不正交,而且, 它们在频域中的距离太近了。另一个问题是, 在相对于使用的标准波特率的符号持续时间内, 它们不支持足够数量的完整周期信号。表2表示每个符号周期相对于使用的标准的脉冲数。

图1 (a) FSK解调信号,(b)正常一体化,(c)在我们的集成技术中更高的噪声裕度。

|

No. |

调制解调器标准 |

载波(Hz) |

1(Hz) |

每个符号周期的脉冲数量 |

0(Hz) |

每个符号周期的脉冲数量 |

信息率 |

双工调制解调 |

|

1 |

ITU-T V.23 |

1700 |

1300 |

1.083 |

2100 |

1.75 |

1200 |

Half |

|

2 |

BELL 202 |

1700 |

1200 |

1 |

2200 |

1.833 |

1200 |

Half |

表2 相对于标准的每个符号周期的脉冲个数

3.1 检测器的实现

在我们的设计中,我们改进了积分器,以便独立于先前的符号,也就是说,在每个符号周期后积分计数器值返回到原来的偏移量。这种改进增加了符号之间的边距, 并在检测中得到更好的结果,在图1(c)中可以看出。该检测器的VHDL代码是基于使用主时钟计数在高电平的接收信号和低电平的计数。同时积分器由两个信号复位,在任何零交叉计数器保存其值并重置为原始偏移。当然,在符号周期结束时,它重置并将在符号持续时间内存储的最大和最小积分值转移到判决设备。

该决策装置减去两个值, 并给出一个相对于查找表的决定。此方法对于任何符号频率和使用的任何M码元都有效。查找表或换句话说, 定义符号的边距是相对于两个因素选择的。第一个是时钟频率相关于波特率和符号频率。第二个是传入信号相位最坏的情况。时钟频率被选择为1.2MHz,即符号持续时间包含1000样本。表3说明了每个标准的设计参数。

第二个因素对于定义相对于判决设备的传入信号最坏的边距情况来说是非常重要的。BELL202标记频率的传入信号作为一个例子, 如图2所示。期间, 传入的信号相位并不时时相同。理想的情况是, 输入信号相位从符号周期开始,如图2(a)所示。在这种情况下,综合器将达到 '高' 和 '低' 的最大值。这意味着定义为一个符号期间的最小持续时间x,将是最大值和等于符号周期的一半。因此,判决设备将具有最大减法输出。另一方面最坏的情况是, 当传入的信号相位被转移,因此x到达1/4的符号期间。这可以在 '高' 状态下完成, 如图2(b),或者 '低' 状态如图2(c)。在这种情况下,积分器达到最终值的一半。因此, 这种情况下的减法输出被视为最小输出。必须选择边距,以使判决设备能够在最坏的情况下做出正确的决定。同时, 符号边界之间必须有足够的距离。图3表示选择指南为选定的 fs 绘制的BELL 202 图。先前的讨论对于提高输出信号的误码率是非常重要的,因为采样频率会影响能量对噪声密度比 (/) 和从等式计算出的误差概率为:

|

No. |

调制解调器标准 |

1(Hz) |

每个符号周期的脉冲数量 |

每一个脉冲取样 |

边缘 |

0(Hz) |

每个符号周期的脉冲数量 |

每一个脉冲取样 |

边缘 |

|

1 |

ITU-T V.23 |

1300 |

1.083 |

923.076 |

650-1000 |

2100 |

1.75 |

571.428 |

520-620 |

|

2 |

BELL 202 |

1200 |

1 |

1000 |

700-1023 |

2200 |

1.833 |

545.454 |

500-600 |

表3 每个标准的设计参数

图2 不同相位输入的FSK BELL202信号。

图三 Fs与F1、F2的相关性

3.2 同步器实现

为了使VHDL代码中使用的所有信号与主时钟同步,我们不得不建立一个非常重要和棘手的电路。该电路的功能是将VHDL设计中的条件从边缘转换为水平。在这一电路中,我们保证了在 '边缘' 检测后的 '水平' 的一个充分的时间段。然后,该条件可以在输出水平上进行。图4显示了时序图、框图和电路示意图的截图。在这个设计中已经使用的这些截图从Mentor工具FPGA Adv.5中捕捉到。我们已经把三个触发器,以确保边缘指示器将是有效的足够时间。如果任何其他应用程序不需要的时间, 我们只可以使用一个带非门的触发器。

3.3 时钟复位实现

由于异步传输,ETS300 标准建议,应在发送任何数据包的开始时发送55Hex 的引导序列, 以使接收机能够恢复符号周期发射机阶段。对于1200波特 BELL202,在发送数据之前, 在信道捕捉后发送额外的150ms 标记位。我们建立了基于55Hex 启动序列传

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[27605],资料为PDF文档或Word文档,PDF文档可免费转换为Word